The European processor project's Rhea chip contains 29 RISC-V cores, and the second phase will begin in January

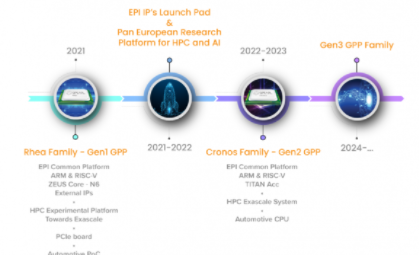

The European Processor Initiative (EPI) has successfully completed its first three-year phase, delivering multi-core chip designs for supercomputers and cars.

The project highlights the transition of Rhea general-purpose processors from ARM to RISC-V, a RISC-V accelerator proof of concept, and an embedded high-performance microcontroller for automotive applications.

The project involves 28 partners from 10 European countries and aims to make the EU independent in high-performance computing (HPC) chip technology.

The successful completion of the first phase, SGA1, paves the way for the second part of the project, which will start in January 2022.

The initial design of the general purpose processor (GPP) was called Rhea and consisted of 72 ARM Zeus processors.

French supercomputer maker Atos is a major partner in the General Purpose Processor (GPP) in collaboration with SiPearl. They defined the architectural specifications for Rhea, which now has 29 cores, uses the RISC-V open instruction set architecture, and is currently done in RTL simulation rather than implemented in silicon. The design is intended for use in supercomputer designs in 2023.

The project states: “With 29 RISC-V cores, the Arm Neoverse V1 architecture SiPearl used to design Rhea will provide an efficient, scalable and customizable solution for HPC applications. Architectural decisions were made following a co-design methodology and by analyzing the performance of advanced IP. SiPearl also optimized the scalable network-on-chip (NoC) to enable high-frequency, high-bandwidth data transfer between cores, accelerators, input/output (IO) and shared memory resources.”

“We are proud to have successfully designed a powerful GPP using cutting-edge technologies and IP built and deployed exclusively by European universities and industry leaders. We are confident that we will soon demonstrate the important role of this GPP in enabling European exascale computing machines, the next breakthrough in HPC that the world is waiting for,” said Emmanuel Ego, Head of Stream at Atos.

"With the launch of the Rhea processor, we are all contributing to ensuring Europe's autonomy in HPC applications such as personalized medicine, climate modeling and energy management," said Philippe Notton, founder and CEO of SiPearl.

The memory controller is one of the most critical IPs in terms of GPP performance. To help evaluate architectural choices, CEA has developed a complete simulation platform with specific instrumentation for analyzing the efficiency of controllers driving high-bandwidth HBM2E memories. The platform allows for efficient analysis of memory device interfaces as all memory commands and data are decoded and traced. The HBM2E subsystem is simulated using multiple random data and instruction patterns for different models and involves all controller functions to maintain HBM2E efficiency.

The chip is also designed with many state-of-the-art embedded security features and key technologies, including an independent Security Management System (SMS) security IP developed by ProvenRun, which provides advanced, Common Criteria certified sovereign security IP for HPC and edge processors.

The University of Pisa contributed a set of cryptographic IPs, called “Crypto Tile”, which SiPearl integrated into the Rhea GPP. This provides the hardware security module with complete security services for high-end symmetric (AES with nine cipher modes), asymmetric (ECC, ECDSA, ECIES, ECDH) and hash (SHA2/SHA3) cryptography, providing several orders of magnitude increase in throughput and reduced energy costs compared to software solutions.

The Crypto Tile also includes secure key storage and secure IP configuration, side-channel attack protection, on-chip true random number generation (TRNG), Linux kernel driver support, extreme key lengths for maximum security, and increased cryptographic throughput thanks to an AXI4-based interface for DMA and Arm or RISC-V programmable cores. Quantum cryptography is also supported.

The European Processor Accelerator (EPAC) test chip proof of concept uses an open source instruction set architecture (ISA) to ensure freedom from proprietary licensing and export restrictions, helping to expand the RISC-V ecosystem and adding to the LLVM compiler database.

The EPAC system and FPGA software development tools leverage the Linux operating system and support popular open source HPC packages such as OpenMP and MPI through community contributions through patches, device drivers, and additional functionality. In addition, parts of the hardware such as STX (Stencil/Tensor Accelerator) were developed using a licensed open source approach around the PULP platform.

"The accelerator streams in EPI are a strong demonstration of the potential of the RISC-V vector approach to transform the world of high performance computing, with a European-designed architecture able to deliver high performance on a low energy budget," commented Stream Leader Jesús Labarta (Barcelona Supercomputing Center). "This work also embodies the European tradition of open science and collaboration. Partners across Europe have joined forces to create what no single organization could achieve alone. By working with open source technologies and projects, EPAC helps expand the RISC-V ecosystem, making this technology viable for an increasing number of applications in the future."

The EPAC vector processing unit (VPU) designed by BSC and UNIZG demonstrates that using the RISC-V long vector architecture for high-performance computing is a viable approach that delivers high performance at a low energy budget and can be scaled up in the future.

The vector units are driven by Semidynamics’ vector-specific Avispado RISC-V cores and Gazzillion Misses technology for energy-efficient processing.

The purpose-built and flexible RISC-V-based many-core Template and Tensor Accelerator (STX), designed by ETH Zurich and Fraunhofer, leverages template processing units to deliver exceptional energy efficiency and programmability for machine learning and template workloads.

Meanwhile, the variable precision accelerator (VRP) designed by CEA improves the efficiency and reliability of scientific high-performance computing applications such as multi-physics simulation.

The EPAC test chip also includes multiple distributed shared L2 caches and coherence nodes (L2HNs) designed by FORTH and CHALMERS, optimized for the high bandwidth requirements of the vector processing units while providing better multi-core programmability.

All processing units and the shared L2HN are connected in a modular fashion through a high-speed NoC, enabling scalability. The test chip also includes advanced SERDES technology for high-bandwidth off-chip and cross-chip communications. Both the NoC and SERDES were designed by Extoll.

The PCB (daughter board) used to test the EPAC test chip was designed and developed by E4 Computer Engineering.

Coordinated by Infineon Technologies, a leader in automotive microcontrollers, Automotive Flow is already paving the way for road-ready autonomous vehicles thanks to a proof-of-concept of an innovative embedded high-performance computing (eHPC) platform and an associated software development kit (SDK). The platform, combined with a scaled-down, automotive-tailored general-purpose processor, meets the growing demand for computing power in future vehicles in a cost-effective, economically viable and functionally safe way.

"Overall, these achievements are a testament to the cooperation, synergy and team spirit that characterize the work of the Automotive Group", said group leader Knut Hufeld (Infineon Technologies). "With its focus on cost-effective, safe and certified automotive solutions, it can be seen as a driver for the overall development of European processors in the HPC field."

The main results were demonstrated on a road-certified BMW X5 vehicle to prove the concept of a groundbreaking eHPC microcontroller unit (eHPC MCU) integrated together with several EPI IPs in a specially designed flexible modular computing platform (MCP). Extensive test drives were conducted to collect data and evaluate test scenarios involving autonomous driving parameters.

Among other features, the platform includes integrated cameras supported by AI and Elektrobit radar imaging analysis software, and comprehensive preparation for using the EPI accelerator in the system. This is the result of a close collaboration between Stream4’s 16 partners to achieve their goal of specifying a suitable eHPC platform, defining its architecture and developing the necessary software development kit (SDK).

Infineon has also extended its automotive microcontrollers in terms of their architecture and performance capabilities, enabling them to act as a master, controlling one or several accelerators, including safety, security, fallback or redundancy. This helps to achieve ASIL-D automotive safety level requirements at the system level, which is required for autonomous driving applications.

The platform is scalable to support future automotive versions of the EPI general-purpose processors, EPAC RISC-V-based accelerators, and Kalray’s Massively Parallel Processor Array (MPPA) accelerators for eHPC, which were developed as an IP in Stream 2.

Test runs have shown that EPI now has capabilities suitable for automated driving, up to at least Level 4.

In addition to the hardware platform, the process also includes the development of a complete software ecosystem, largely based on software products from automotive software specialist Elektrobit. This area also includes the automotive eHPC platform software stack, including classic automotive open operating system architecture (AUTOSAR) development for Auto eHPC MCUs, as well as adaptive AUTOSAR development for HPC GPP and L4Re hypervisors (virtualization), which are critical for automotive applications.

Previous article:Ceramic Speed Selects Syntiant for Edge AI Predictive Maintenance

Next article:Could RISC-V be the choice for eight-bit MCUs?

Recommended posts

- Does anyone have a detailed tutorial on Cadence 16.6 Allegro PCB package drawing?

- ThetutorialsontheInternetareincomplete.Forexample,afterplacingthepinpadsonthechippackage,Icannotplacethecenterpad.Ididnotfindanytutorialsonhowtoplacethecenterpad. https://download.eeworld.com.cn/eewsearcher?kw=

-

梅花飘落孤人醉

PCB Design

PCB Design

- [LDO common terms 1] line regulation and load regulation

- LineRegulation 1.Definition:Alsoknownassourceeffectorgridregulation,itreferstothefluctuationofoutputvoltagewithlinearchangeofinputvoltage,undertheconditionoffullload.(Wheninputvoltagechangeswithintheratedran

-

zch_genius

Power technology

Power technology

- Say goodbye to film! Design a smarter car sunroof

- Thankstonewtechnologyforfuturevehicles,sunroofsandcarwindowtintsarenowprogrammablefeaturesinyourcar.Attheturnofaswitch,youcannowblockthelightcomingthroughyourcar'ssunrooforenjoythestarryskywhiledrivingatn

-

zqy1111

TI Technology Forum

TI Technology Forum

- The combination of software and hardware - "Infrastructure in the era of big models - Chapter 2"

- DesigningGPUsforparallelcomputingisnolongerasecret,andmanymanufacturerscandoit.However,thedifficultyliesinthesoftwareecosystem.NVIDIAhasdevelopedCUDA,aparallelcomputinglibrarythatcantransfertraditionalcomputin

-

superleon123

Special Edition for Assessment Centres

Special Edition for Assessment Centres

- Exploiting software vulnerabilities! 19-year-old boy remotely hacked into Tesla

- ResearchersfromseveralcybersecuritycompanieshaveproventhatTeslacanbeeasilyhacked. DavidColombo,a19-year-oldGermansecurityresearcher,saidrecentlythathefoundasoftwarevulnerabilityinTesla'ssystemandus

-

赵玉田

Security Electronics

Security Electronics

- 2024 DigiKey Innovation Contest: Smart Connected Speakers

- 1.Introduction Thepurposeofthisenvironmentprojectmoduleistoassignwiredspeakerstowirelesswifispeakers. AudiotransmissioncanbeachievedunderthesameLAN UseKugouAudiotopushmusiconmobilephones 2.SystemBl

-

rertet

DigiKey Technology Zone

DigiKey Technology Zone

- Popular Resources

- Popular amplifiers

- Why is the vehicle operating system (Vehicle OS) becoming more and more important?

- Car Sensors - A detailed explanation of LiDAR

- Simple differences between automotive (ultrasonic, millimeter wave, laser) radars

- Comprehensive knowledge about automobile circuits

- Introduction of domestic automotive-grade bipolar latch Hall chip CHA44X

- Infineon Technologies and Magneti Marelli to Drive Regional Control Unit Innovation with AURIX™ TC4x MCU Family

- Power of E-band millimeter-wave radar

- Hardware design of power supply system for automobile controller

- Driving Automation Safety and Economic Engineering

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Intel promotes AI with multi-dimensional efforts in technology, application, and ecology

- ChinaJoy Qualcomm Snapdragon Theme Pavilion takes you to experience the new changes in digital entertainment in the 5G era

- Infineon's latest generation IGBT technology platform enables precise control of speed and position

- Two test methods for LED lighting life

- Don't Let Lightning Induced Surges Scare You

- Application of brushless motor controller ML4425/4426

- Easy identification of LED power supply quality

- World's first integrated photovoltaic solar system completed in Israel

- Sliding window mean filter for avr microcontroller AD conversion

- What does call mean in the detailed explanation of ABB robot programming instructions?

- Europe's three largest chip giants re-examine their supply chains

- Breaking through the intelligent competition, Changan Automobile opens the "God's perspective"

- The world's first fully digital chassis, looking forward to the debut of the U7 PHEV and EV versions

- Design of automotive LIN communication simulator based on Renesas MCU

- When will solid-state batteries become popular?

- Adding solid-state batteries, CATL wants to continue to be the "King of Ning"

- The agency predicts that my country's public electric vehicle charging piles will reach 3.6 million this year, accounting for nearly 70% of the world

- U.S. senators urge NHTSA to issue new vehicle safety rules

- Giants step up investment, accelerating the application of solid-state batteries

- Guangzhou Auto Show: End-to-end competition accelerates, autonomous driving fully impacts luxury...

- Using TI power timing controller in 5G MIMO application

- Design of 8-bit RISC CPU in FPGA

- MCU development full-time/part-time and sales assistant

- MAX10 pin crosstalk

- [RVB2601 Creative Application Development] Practice 4 - Keyboard Control of Network Music Playback

- Download the information to win a Jingdong card | Tektronix's innovative new generation touch screen oscilloscope

- G100 acoustic imager is used in many product development and fault diagnosis fields

- EEWorld invites you to dismantle (fifth issue): dismantle Xiaomi fast charging power strip

- Detailed explanation of the two methods of noise figure measurement, do you get it?

- P&SM99@%S34 VR8H6-RONJ.pdf

CLC114AJP

CLC114AJP

京公网安备 11010802033920号

京公网安备 11010802033920号