NAND flash memory has been around for so many years, and its development has never stopped. Basically, it has been pursuing higher storage density. Therefore, from the initial SLC to the current QLC, although the storage density has been greatly improved, in terms of performance, the original SLC is still faster. At the 2020 Flash Memory Summit, Andy Hsu, CEO and founder of NEO Semiconductor, introduced their company's new X-NAND flash memory architecture, which is expected to combine the speed of SLC with the high density and low price of QLC.

The news comes from tomshardware, which claims that X-NAND's random read and write are three times faster than QLC flash memory, continuous read is 27 times faster, and continuous write is 14 times faster. In terms of performance, it is indeed very fast.

In addition, the chip size is smaller, and the die size is only 37% of the same 16 planes NAND flash memory, which allows better flexibility and can reduce the chip size according to actual needs. Moreover, X-NAND still has high parallelism in a smaller size, just like what you see on smartphones or M.2 SSDs. This can be achieved without affecting durability and cost, and its power consumption is very low.

Today's QLC SSDs rely heavily on SLC Cache, because the original write speed of QLC is too low, so QLC SSDs basically use its capacity advantage to equip large-capacity SLC Cache. In the consumer market, the write pressure is usually not very high, so there is enough free time to move the SLC buffer to the QLC flash memory for storage, but there is no such time for enterprise-level loads. X-NAND allows SLC and QLC write modes to be performed simultaneously, so that the flash memory can always maintain the performance of SLC.

Western Digital predicts that QLC's share of the flash memory market may be as high as 50% by 2024. The design goal of X-NAND is to ensure the use of existing NAND solutions. Traditional NAND processes do not require structural changes, have no additional manufacturing costs, and can be developed through rapid sampling. The design aims to accelerate the promotion and application of QLC, especially in the data center market, so that QLC performance is no longer a bottleneck.

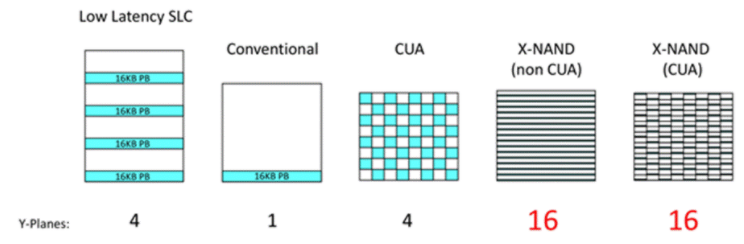

At the same time, X-NAND has modified the programming and erasing strategies to improve the durability of QLC flash memory. X-NAND changed the page buffer from 16KB to 1KB, but the size of the Plane can be increased by 16 times.

Plane is the smallest unit of flash memory. There is one or more Planes in each Die. The page buffer stores the data stored between the bus and the flash memory. Flash memory chips are divided into Planes that protect bit lines or cell strings, so Plane division can reduce the length of the bit lines, which helps improve performance. This technology can be further enhanced by shielding between adjacent bit lines to reduce the setup time when reading or verifying programming. Since up to sixteen bit lines can be programmed in parallel, write performance is improved.

X-NAND has six main features: multi-bitline write, multi-plane QLC programming, program suspend, multi-BL read, single latch QLC read, and SLC/QLC parallel programming. Depending on the implementation, the program throughput can be greatly improved because multiple planes can be used in the programming sequence.

Using multiple banks allows for simultaneous SLC and QLC programming, ensuring that SLC pages are never full while data can be transferred to QLC pages at SLC speeds. Programming allows for the use of internal shared inter-page buffer data lines or I/O buses to minimize additional latency. Reads are improved by using Plane latches to read each bit line, and data can be refreshed in a non-destructive manner like DRAM.

X-NAND can be used with any number of existing NAND, which increases flexibility and simplifies conversion. NEO Semiconductor hopes that the technology will be cost-effective, fast and easy to implement in existing designs. The company said it is particularly useful for high-density flash memory like QLC because it can take advantage of high capacity, high performance and small chip area, while having good endurance and power consumption. The technology targets embedded devices, AI and cloud, including NAS, data centers and edge computing.

Previous article:SK Hynix's Acquisition of Intel NAND: Changes in the Storage Industry

Next article:TechInsights envisions the future of 3D NAND flash memory

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- The role of adding a reverse diode to the be pole of the transistor

- Sub-library: Motion Algorithm Library

- TI radar technology is changing three trends in the in-cockpit sensing market

- Serial port expansion

- HR made inappropriate remarks in the circle of friends, made a public apology, and was fired!

- 【AT-START-F425 Review】No.02 AT32F425 Development Environment Construction

- About the use of AWR1642BOOST development system

- Excellent "Internet of Things" (IoT) video recommendation, it explains it very thoroughly!

- Design of TPS53355 ripple injection circuit

- Latches and Flip-Flops

Electrical Control and PLC (Wang Jianping and Zhu Chenghui)

Electrical Control and PLC (Wang Jianping and Zhu Chenghui) KA-SLC-O801 lighting template

KA-SLC-O801 lighting template

京公网安备 11010802033920号

京公网安备 11010802033920号