In recent years, more and more fields require high-performance, highly integrated DSP devices, and the demand for DSPs from multimedia processors with increasing functions has also increased dramatically. As a result, integrated chips based on the MCU+DSP architecture have emerged. Lower costs, smaller packages, and lower power consumption have opened up a "sunny road" for DSP or MCU manufacturers, and in the future, they will continue to move forward along this new path. This series of articles will introduce you to the more popular processors or solutions based on the MCU+DSP architecture on the market.

Freescale DSP56800E

Freescale has been deeply involved in the field of DSP and MCU for several years. To meet the needs of market development, the company took the lead in launching a new generation of enhanced core 56800E based on the 56800 core. This product can provide dual functions of DSP and MCU on a single core. The 56800E series DSP will provide low-power, low-cost single-chip solutions for the growing industrial, motor control, automotive and converged communication and data communication market applications. Because this single-core design consumes less power, Freescale has enabled a large number of new battery-powered portable applications that require signal processing functions, such as portable digital audio, Internet devices and PDAs. Recommended information related to

DSP56800E :

1. MC56F8335: Digital signal controller based on 56800E core

2. Three-phase BLDC motor control based on 56800E digital signal processing and Hall sensor

Introduction

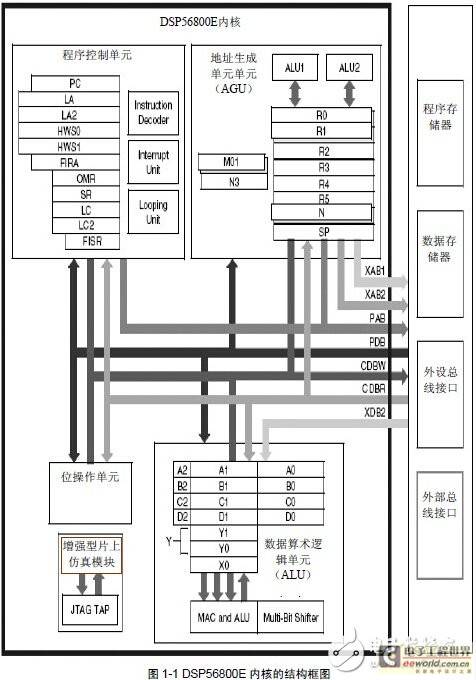

Compared with 56800, the performance of 56800E can be improved by up to 5 times, providing a clear product migration path for customers who need more storage space, higher code compilation efficiency and higher MIPS performance. DSP56800E consists of several functionally independent modules. Including: data arithmetic logic unit (ALU), address generation unit (AGU), program controller, bit operation unit, enhanced on-chip simulation module (Enhanced OnCE) and system bus. As shown in the figure.

Flexible memory mode is a major feature of the DSP56800E architecture, including the following aspects:

Program RAM and ROM modules

Data RAM and ROM modules

Non-volatile memory (NVM) modules

Boot ROM, module that executes code in the boot RAM area

Freescale's standard on-chip peripheral interface bus (IP-BUS) supports a variety of on-chip peripheral modules, including the following modules:

Phase-locked loop (PLL) module

16-bit timer module

Watchdog (COP) module and real-time timing module

Synchronous Serial Interface (SSI) Module

Serial Peripheral Interface (SPI) module

Programmable general purpose I/O (GPIO) module

characteristic

The DSP56800E architecture has a series of new features to improve system performance, reduce application costs, and simplify product development, including the following aspects.

High performance: DSP56800E supports many DSC applications.

Compatibility: Backward compatible with the source code of the DSP56800 series. The DSP56800 only needs to be recompiled or reassembled to run on the DSP56800E system.

Easy Programming: The instruction mnemonics of DSP56800E are similar to those of MCU, making it easy to switch from traditional microcontroller programming to DSC programming. To optimize the execution of algorithms, the instruction set of DSP56800E supports both decimal and integer types.

Support for high-level languages: Programs written in C language are very suitable for the DSP56800E structure. Most applications can be written in high-level languages without affecting the performance of the DSC. The flexible instruction set and programming mode make it possible to generate efficient compiled code.

Rich instruction set: In addition to the instruction set that supports the DSC algorithm, the DSP56800E also provides control, bit operation and integer processing instructions, and supports multiple data types and addressing modes, allowing users to easily generate efficient and compact code.

High code density: The basic single-word instruction length of DSP56800E is only 16 bits, while multi-word instructions are used for more complex operations to achieve optimized code density. The DSP56800E instruction set emphasizes efficient control programming, because the largest part of an application is this operation.

Support multitasking: It is easier to execute a real-time operating system or a simple multitasking system on the DSP56800E than on other DSC chips. The DSP56800E fully supports software stacks, fast 32-bit context switching from the system stack, basic test and setup instructions, and four-priority software interrupts.

Precision: DSP56800E has the ability to perform precise calculations.

Hardware loops: The DSP56800E provides two types of hardware loops greater than 0. This improves performance and eliminates the need to use unrolling loop techniques.

Parallelism: Each on-chip execution unit, memory device, and peripheral operation is independently processed in parallel. Due to the high parallelism, the following operations can be executed in parallel within 1 instruction:

— Get the next instruction

- 16-bit multiplication by 16-bit and adding the result to a 36-bit number

- Optional inversion, rounding and saturation processing

- 2 16-bit moving

—Unloaded hardware loop

—Update of 2 address pointers

Invisible instruction pipeline: The eight-stage instruction pipeline improves system performance while remaining invisible to the programmer. Developers can use high-level languages without having to consider the pipeline.

Low power consumption: Due to the use of CMOS technology, the DSP56800E consumes very little energy, and the DSP56800E supports two more power-saving modes, STOP and WAIT modes. The power management module can shut down those parts that are not used logically.

Real-time debugging: Freescale's enhanced on-chip emulation technology provides a simple, low-cost, non-intrusive, speed-independent way to access the state of the DSP56800E core. By using this technology, programmers can fully control the operation of the processor without stopping the core, and can complete debugging tasks simply and quickly.

The DSP56800E's efficient instruction set and bus architecture, extended parallelism, on-chip programming and data memory, and advanced debugging and testing capabilities enable the core to address real-time issues, embedded DSC, and control tasks.

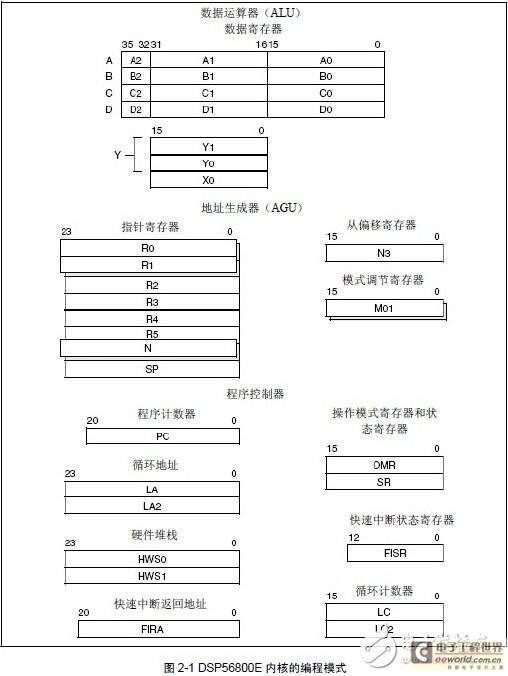

Kernel Programming Model

The core registers of the DSP56800E are considered part of the core programming mode. As shown in Figure 2-1. The registers of the on-chip modules are mapped to 64 cells of data memory. Note that these 64 cells can be located anywhere in the data memory on a specific device. An example of using memory blocks is shown in Table 2-1. You can refer to the user manual of the specific device for a detailed description of its modules, including their functions, the registers of the storage area and their location mapped to memory.

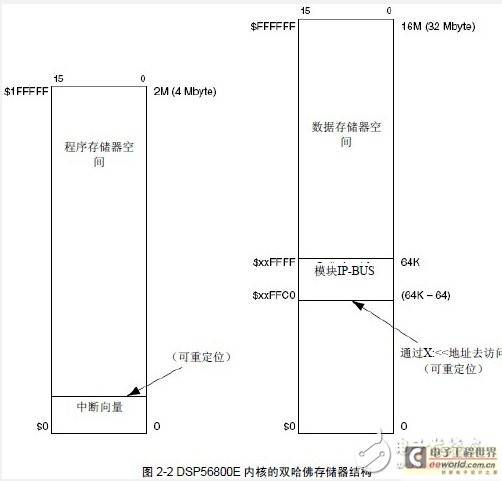

Dual Harvard Memory

DSP56800E has a dual Harvard structure with separate program storage area and data storage area, as shown in Figure 2-2. This structure allows simultaneous read and write operations on the program storage area and data storage area, and the data memory supports simultaneous read operations of 2 addresses and supports memory operations of up to 3 address units.

In the program memory, there are reset and interrupt vectors of any size and location. The peripheral registers are mapped to the address units of 64 words in the data memory.

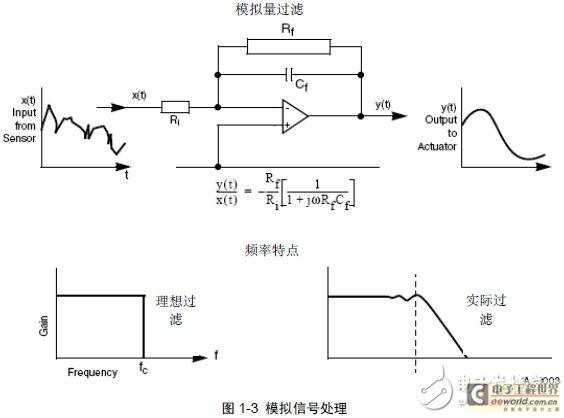

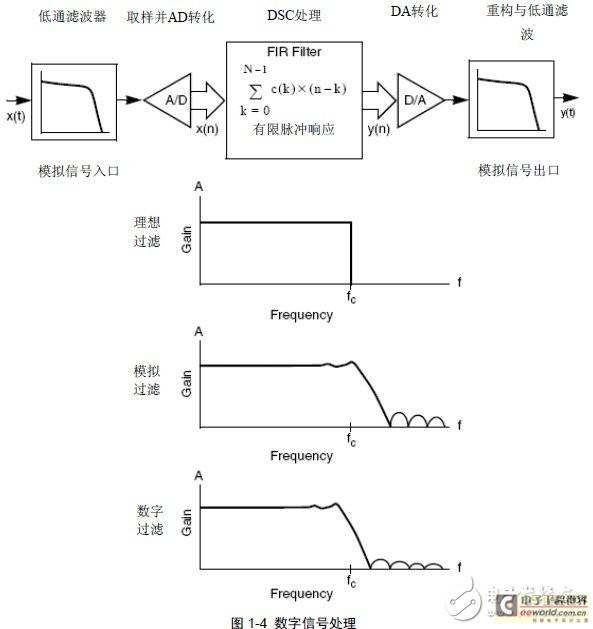

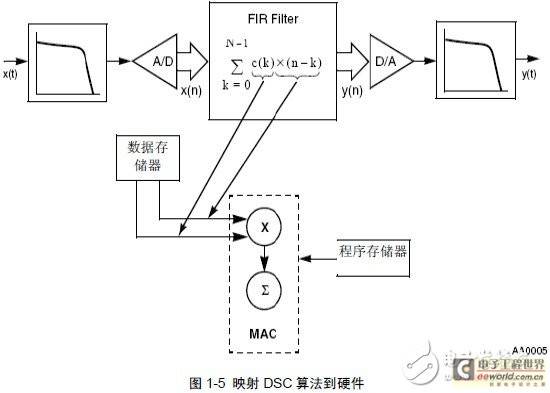

The 64-word address units of the peripheral registers can be remapped to any address in principle. In order not to overlap the RAM and ROM data storage blocks, the addresses of the 64-word units are usually set specifically. The X:< Note that the top 12 cells of the 64 cells are reserved for use by the DSP56800E core for interrupt priority and bus control registers. DSC Examples A DSC is a processor that can perform arithmetic on real-time signals that are periodically sampled and digitized. DSC instances all include the following aspects: Filtering Convolution (mixing two signals) Correlation (comparing two signals) Rectification, amplification and transmission Figure 1-3 is an example of analog signal processing. The circuit in the figure filters the signal from the sensor. The sensor signal acquisition circuit uses an adjustable amplifier and uses the result to control a power arm. It is impossible to design an ideal filter. Engineers must try to meet the following factors when designing filters: acceptable responsiveness, changes in different temperatures, component aging, power supply fluctuations, and component accuracy. Circuits designed according to such requirements generally have low anti-interference performance, require frequent parameter adjustments, and are difficult to modify. The equivalent circuit using DSC is shown in Figure 1-4. This application requires an A/D converter and D/A converter in addition to the DSC. The processing circuit in the figure above first limits the input signal band through a filter to remove interference signals that exceed the band. Then the signal is sampled, digitized through an AD converter and sent to the DSC for digital processing. The output of the DSC is converted into an analog signal through a DA and low-pass filtered to eliminate the impact of digitization. The specific filtering performed by the DSC is strictly a software process. The DSC can perform any filter that can be implemented using analog techniques. Furthermore, adaptive filtering that is difficult to achieve using analog techniques can be easily implemented using the DSC. In summary, the advantages of using DSC are as follows: Fewer components Stable, deterministic performance No need to adjust filter coefficients Wide range of applications More distinct filtering characteristics Strong noise immunity Easy to implement adaptive filtering With self-test function Better power interference resistance mechanism The DSP56800E series is not a customized IC chip for a specific application, but rather a general-purpose DSC architecture for efficiently executing common DSC algorithms and control codes. As shown in Figure 1-5, the key properties of DSC are as follows: Multiply-Accumulate (MAC) Operation Each instruction cycle of MAC takes 2 operands Powerful instruction set ensures execution flexibility Move DSC data in/out MAC operation is a basic operation in DSC. The dual Harvard structure of DSC56800E optimizes MAC operation. By accessing two independent data units at the same time, multiplication and addition operations can be completed in one MAC clock cycle. The whole process must be under the control of the program to complete the data acquisition from the multiplier and the transfer of the calculation results. Since the memory and MAC are independent of each other, DSC can perform data exchange between two memories, a multiplication and addition operation, and the update of two addresses in one instruction, so that many DSC-level processors can perform multiplication operations more efficiently.

Previous article:High reliability analysis and design of intelligent controller based on DSP

Next article:Switching Inverter Power Supply Based on DSP

Recommended ReadingLatest update time:2024-11-16 19:52

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 10 ways to dissipate heat from PCB!!!

- LOTO Lesson 3: Frequency Response Curve Plotting --- 3 groups of RC low-pass filter tests with different parameters

- Three major programming languages for the development of the Internet of Things

- [Shanghai Hangxin ACM32F070 development board + touch function evaluation board evaluation] Transplant RT-Thread Nano

- Since it is so similar to inductors, why can you only use ferrite beads in your circuit?

- Device tree interrupt node

- Can CC2541 support 10 external interrupts?

- PCB failure analysis and some cases

- Evaluation report summary: Nengdian Technology capacitive and photoelectric liquid level sensors

- ADRV9002 Dual Narrow Bandwidth RF Transceiver

Modern arc welding power supply and its control

Modern arc welding power supply and its control

京公网安备 11010802033920号

京公网安备 11010802033920号