Functions such as user comfort, safety, and ADAS (driver assistance) are continuously increasing the number of electronic control units (ECUs) in vehicles. However, the continuous expansion of ECUs has brought more challenges to automakers. Therefore, most automakers around the world are transitioning from traditional distributed ECU architectures to domain- or zone-based ECU architectures.

The domain-based architecture aims to integrate high-level control for a complete domain (Figure 1-a). Especially in hybrid and electric vehicles (HEV and EV), all functions interact closely, and distributed architectures have difficulty managing the complexity and real-time nature of the system. For example, the operation of an electric vehicle when braking is not only to control the brakes, but also to capture energy to charge the battery.

Figure 1-a Domain-based architecture aims to integrate higher-level control. Source: STMicroelectronics

Figure 1-b: A region-based architecture consolidates multiple ECUs onto a single MCU. Source: STMicroelectronics

The region-based architecture combines multiple ECUs from multiple domains onto a single MCU and reduces the number of wires throughout the vehicle (Figure 1-b). There are two main factors driving OEMs to reduce wires in their vehicles: Every additional wire harness adds weight and complexity to the vehicle. Weight is key because it reduces vehicle range. The region-based architecture has a major advantage in eliminating some wire harnesses, especially in the body area. But that's not all: the vehicle can use different architectures for different domains to flexibly take full advantage of both domain and region architectures.

Both zone-based and domain-based architectures support loose coupling of hardware and software lifecycles. Both allow manufacturers to update and upgrade vehicle software without changing components. These new architectures also provide software-defined vehicles, which can launch new features and vehicles in the shortest possible time.

Changes in memory requirements due to architecture conversion

First, domain and regional architectures require MCUs that offer higher computational power than those used in traditional distributed architectures. Today’s domain architectures require multi-core real-time MCUs running at clock speeds up to 400 MHz. In fact, some MCUs in these architectures have up to 6 Arm Cortex-R52 cores, with up to 4 of them running in a lockstep configuration to perform real-time error checking, for a total of up to 10 Arm cores.

Although MCU core and operating frequency are commonly referenced specifications by system architects, embedded/onboard non-volatile memory (NVM) also has a significant impact on overall system performance and cost. Despite this, memory specifications are the most easily overlooked. For example, two MCUs with the same core and operating frequency may have significant differences in computing and power performance and reliability due to the type of memory they use and its speed. Memory type and memory speed also contribute to the MCU's firmware upgrade capabilities, cost, and power consumption.

Embedded non-volatile memory limitations of new architectures

Typically, in computing systems, non-volatile memory is used to store code and data. Most general-purpose MCUs use embedded flash for this purpose. And this embedded flash is usually floating gate or some kind of charge well NOR flash. Most of these embedded NVMs are very slow, supporting a maximum frequency of even less than 20 MHz.

For a 25-MHz NVM in a 400-MHz system, the memory requires approximately 15 wait states. Therefore, even though the CPU is running at 400 MHz, it takes 15 cycles to fetch instructions from memory before the CPU can execute them. MCUs use caches to minimize these wait states, but frequent cache misses can have a significant impact on overall computing performance.

Over time, innovation has improved embedded NOR flash speeds. Unfortunately, flash technology has been difficult to scale to smaller technology nodes. Most NOR is currently manufactured at 40 nm, with a few at 28 nm, and it is difficult to integrate these memory cells into very complex high-k metal gate technology.

Most of today’s zone-control-based MCUs are developed at the 28 nm node to maximize integration and allow for larger memory needed to support very large applications. These can be 20 MB or larger in zone and domain architectures. But over-the-air (OTA) firmware upgrades (more on OTA firmware upgrades in Part 2 of this series) require these MCUs to provide at least 40 MB of embedded NVM to support this functionality.

That’s why such memory capacity may not be practical at 28 nm for most available embedded flash technologies. In addition, some other scalable embedded NVM technologies cannot meet the high temperature conditions required for automotive applications. Therefore, some regional control MCUs either have no embedded NVM or are available as a two-chip system-in-package (SIP). These MCUs usually have larger RAM and import code execution into RAM.

Although this solution provides slightly better computing performance than embedded flash, it has some disadvantages for executing zone- and domain-based applications.

The first disadvantage is the long boot time required for the MCU to load the contents of the RAM at startup. While it is tolerable for an infotainment system to take a little time to boot up when the vehicle is turned on, the extended boot time is a major issue for domain and regional architectures that manage door control, steering control, lighting, and other critical functions; users expect these to be available immediately. Another disadvantage of RAM is that it consumes more power than NVM.

Additionally, retaining RAM while in low-power mode requires constant power for memory refresh. When the data in RAM is not needed and can be powered off, reloading the data when transitioning from low-power mode to active mode comes at the expense of longer transition times, which may not be acceptable in some applications. If the application frequently transitions to active mode, the power budget for reloading RAM is significant and may defeat the purpose of low-power mode.

Another consideration is system cost. RAM is a relatively area-intensive IP. Therefore, putting a large RAM into the MCU to run the application code will be more expensive than embedded NVM. Then, whether the external NVM is integrated into the package itself as a SIP or mounted on the board, it will increase the cost and make the system more expensive. Other disadvantages include system and supply chain reliability.

In a system, RAM has a higher bit flip rate than NVM - usually due to radiation, commonly referred to as soft error rate (SER). This affects the reliability of the system. To support the highest level of reliability, the latest MCUs for automotive applications support end-to-end error correction code (ECC). External NVM does not support end-to-end ECC, which results in reduced reliability and requires additional mitigation techniques for safety-critical ECUs.

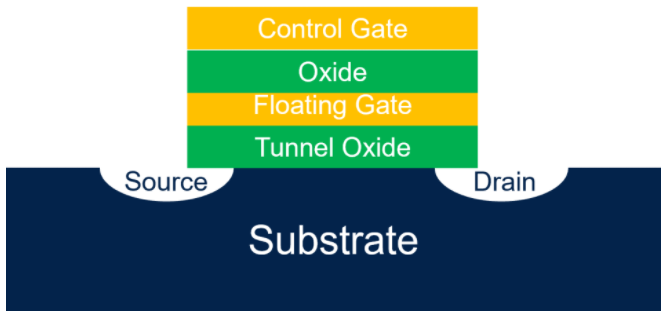

At the same time, data memory requires higher endurance than program memory. This higher endurance requirement also brings challenges. For example, in a floating-gate NOR cell, a tunnel oxide separates the floating gate from the channel (Figure 2).

Figure 2. The tunnel oxide separates the floating gate from the channel in a floating-gate NOR cell. Source: STMicroelectronics

With each write and erase cycle, this oxide degrades and leakage increases, causing the flash to age and become unsuitable as data storage. Scaling the technology to smaller nodes exacerbates this problem. Not scaling the tunnel thickness has its own side effects, as large memory blocks embedded in smaller technology nodes still take longer to read, write, and erase.

Embedded flash memory also takes a long time to write, partly because it must be erased before writing. All of these factors can have an adverse effect on system performance, especially when the CPU can run at high frequencies and memory read and write waits become a bottleneck.

Advantages of PCM in regional and domain architectures

The embedded phase change memory (ePCM) provided in the Stellar SR6 device meets the performance requirements of regional and domain MCUs. Figure 3 shows a cross-section of an ePCM cell in FD-SOI technology.

Figure 3 PCM cell. Source: STMicroelectronics

A key point that affects the current generation of regional MCUs and the entire technology and cost roadmap is that the integration of ePCM memory elements in automotive applications is much cheaper than 28 nm embedded flash technology. In addition, the integration of ePCM does not interfere with the complex high-k metal gate transistor structure at all.

Finally, unlike embedded flash, write operations in ePCM do not require high voltages. Therefore, ePCM can work with standard transistors, while flash requires dedicated high-voltage transistors to manage write voltages that may be 10 V or more. All of these factors affect manufacturability and cost.

Unlike NOR or NAND flash, PCM works based on the resistivity change of a Germanium Antimony Telluride (GST) alloy. This alloy changes resistivity in response to rapid temperature changes, and the resistivity determines the state of the memory. Figure 4 shows how a SET or RESET occurs in PCM.

Figure 4 The PCM write process shows how bits are set or reset. Source: STMicroelectronics

As a result, ePCM provides fast read and write times compared to embedded NOR Flash. Write times are significantly reduced because ePCM does not require an erase operation before writing. This feature also significantly reduces factory programming time, thereby reducing manufacturing costs.

In addition, ePCM offers reliability and endurance advantages comparable to embedded flash. At the same time, ePCM allows for the single-bit changeability of emulating true EEPROM, which further significantly reduces system write time. In addition, since it only operates on the target bit, single-bit writes do not affect the life of adjacent storage cells. Therefore, even with an endurance level comparable to embedded flash, PCM effectively allows for more writes to the emulated EEPROM in the data NVM.

Previous article:Arm's new automotive image signal processor accelerates the introduction of driver assistance and automation technologies

Next article:congatec launches x86-based COM-HPC server for autonomous vehicles

Recommended ReadingLatest update time:2024-11-16 22:36

- Popular Resources

- Popular amplifiers

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- The channel for exchanging TI points for chip points has been opened. Full redemption within a limited time. The ultimate redemption is coming~

- An error occurred when simulating and debugging the program: no contex-m device found in jtag chain. How to deal with it?

- GPIO principle of TMS320F28335

- Oh my god, the teacher actually organized a high school student to take the college entrance examination for him (photo)

- Introduction to the working principle and characteristics of rectifier transformer

- TD1509 has large output voltage ripple

- Design of data forwarder based on MSP430F149

- [Evaluation of EC-01F-Kit, the NB-IoT development board of Anxinke] 01. Communication test

- Mini Adafruit QT Py Development Board

- openmv3 serial port hangs up

Monocular semantic map localization for autonomous vehicles

Monocular semantic map localization for autonomous vehicles

京公网安备 11010802033920号

京公网安备 11010802033920号