In recent years, digital television technology has developed rapidly. Digital video mixers can mix two or more digital video signals into one or more digital video signals according to certain algorithms. As the basic processing unit of digital video signals, the mixer plays a vital role in the editing, production, broadcast control and transmission system of digital TV programs.

The digital video keying mixer based on single-chip microcomputer control introduced in this paper has the following characteristics: it contains two-stage series keying mixer, which can input two additional digital signals into the main signal, such as clock logo or various subtitle logos; it can be remotely controlled or controlled by buttons on site; the system configuration can be updated and saved at any time, and the system functions and technical parameters can be changed; the system is stable and reliable, and has the ability to self-reset in the event of abnormal phenomena such as power failure and freeze.

The whole system consists of two parts: hardware and software. The hardware includes a digital mixing part and a single-chip microcomputer control part.

1 Digital mixing section

The input digital signals include background signal, key signal and filling signal, and the output is three digital signals and one analog signal. The hardware block diagram of the digital mixing part is shown in Figure 1.

The GS9020A [2] serial digital video input processor is specially designed to receive SMPTE 259M serial digital signals. It has error detection and processing capabilities to ensure the integrity of serial data; it can be directly connected to the GS9035A or GS9025A, and provides an 8-bit parallel port and an I2C serial port to communicate with an external microprocessor. This system reads and configures the GS9020A status through the I2C bus .

TMC2081 [3] is a digital video processor that can mix digital video in GBR, YCB, CR or color sequence formats in proportion. Under α channel control, it can perform simultaneous fade-out and fade-in functions according to M = (α) V 1 + (1-α) V 2 (0 ≤ α ≤ 1). TMC2081 provides microprocessor I/O ports.

The error detection and handling coprocessor GS9021 [4] performs error detection and handling according to SMPTE RP-165. It can interface with the GS9002, GS9022 or GS9032 serial digital encoder to generate horizontal synchronization, vertical blanking and field sequence signals. It provides an 8-bit parallel port and an I 2 C serial port to communicate with an external microprocessor. This system reads and configures the GS9021 status through I 2 C.

The CMOS chip SAA7121 is a digital video encoder that encodes digital brightness and color difference signals into CVBS and S-video analog signals simultaneously, and also supports NTSC-M, PAL B/G and sub-standards. The input signal can be YCBCR (CCIR 656) or MPEG decoded data; there are three digital-to-analog converters for Y, C and CVBS. The basic encoding function consists of subcarrier generation, color modulation and synchronization signal interpolation. SAA7121 provides an I2C bus interface and can work in active or slave mode. This system configures SAA7121 through the I2C interface.

2 MCU control part

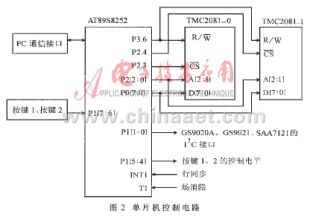

The control circuit based on the single-chip microcomputer is shown in Figure 2. It completes the following functions: serial communication with the PC to transmit commands and data; read and write TMC2801 through the 8-bit parallel interface; read and write SAA7121, GS9020A and GS9021 through the I2C bus; save and update system configuration data; key control function, press the key to display or not display additional digital signals.

2.1 AT89S8252 MCU

AT89S8252 [6] is an 8-bit CMOS microcontroller produced by ATMEL, which is compatible with the MCS-51 series. Its main features include 8K bytes of FLASH program memory (ROM), 2K bytes of on-chip EEPROM, 256 bytes of internal data memory (RAM), three 16-bit timers/counters, SPI serial interface and watchdog timer.

The reasons for choosing AT89S8252 are: the on-chip EEPROM can save data and will not lose it when the power is off; the watchdog has the ability to self-reset in the event of abnormal phenomena such as power off and freeze, which can improve the stability of the mixer; and it is compatible with the MCS-51 series.

2.2 Communication Interface

The communication interface provides RS-485 standard, and the interface circuit is mainly composed of MAX488 (RS-485 receiver and transmitter). RS-485 standard is not only compatible with RS-232, but also suitable for long-distance data transmission.

3 Software Design

According to the requirements of the single chip control function, the software consists of two parts: the main program and the serial port interrupt subroutine. The main program flow chart is shown in Figure 3. The programming focuses on: mixer initialization; key control function; judgment and execution of PC commands; updating system configuration and saving data.

3.1 Access EEPROM and watchdog settings

AT89S8252 has a watchdog and EEPROM control register WMCON.

WMCON EQU 96H ;WMCON address

; Write one byte

SETB WMCON.3 ;Access EEPROM enable

SETB WMCON.4 ; Write EEPROM enable

MOVX @DPTR, A; write one byte, addressing range 0000H~07FFH

JNB WMCON.1, $; WMCON.1 is 1, ready for next access

CLR WMCON.4

CLR WMCON.3 ;MOVX instruction can access external data memory

Reading bytes from EEPROM is similar to writing.

WMCON.0 is the watchdog enable bit, WMCON.1 is the watchdog reset bit (1 after the MCU is reset), and WMCON.5~7 can set the watchdog clock cycle (16~2048ms). If the watchdog reset bit is not set or the watchdog is not turned off within the watchdog clock cycle, the internal reset signal will reset the MCU.

3.2 Serial communication with PC

There are three data formats for communication between PC and MCU: command length + command number; command length + command number + read data byte number N + first address + checksum; command length + command number + write data byte number N + first address + data 1 + ... + data N + checksum. Command length, command number, read and write data byte number N, first address and data n (1≤n≤N) are all one byte, expressed in hexadecimal. Command length is the number of bytes in the entire command format. Checksum = command number

read data byte number N

first address, or checksum = command number

write data byte number N

first address

data 1

...

data N. For example: to display the additional digital signal 1 and turn on LED No. 1, the PC sends 0x02 0x01; to read the 00-03 control memory of TMC2081 No. 1, the PC sends 0x5 0xB 0x4 0x0 0xF; to write 0x0 0x21 0x1D 0x0 to the 27-2A memory of SAA7121, the PC sends 0x9 0xC 0x4 0x27 0x0 0x21 0x1D 0x0 0x13.

In the serial port interrupt subroutine of the microcontroller, it is determined whether a complete command format is received based on the received command length. If a complete command format is received, the flag FLG1 is set (as shown in Figure 3). According to this flag, the program for processing PC commands in the main program is entered, and the commands sent by various PCs are identified by the received command number. For example, command No. 1 is to display the additional digital signal 1 and light up LED No. 1, and command No. 0xC is to write to the SAA7121 memory, etc. Based on the received checksum, the correctness of the received PC data can be determined to prevent incorrect operation of the mixer.

Design software with VB6.0 to read and write the serial port of PC. The baud rate of this article is 9600bps, and the timer/counter 2 (T2) of the microcontroller is set in the working mode of baud rate generator.

3.3 Accessing TMC2081

TMC2081 provides microprocessor I/O ports, including read/write control R//W, chip select /CS, register select control A[2:0], and data I/O port D[7:0]. Through the microprocessor I/O port, the internal control memory of TMC2081 can be accessed to complete the configuration of the chip. The read and write timing is shown in Figure 4.

The shortest required time of parameters t PWLCS , t SA , t SD , t HD , t PWHCS , t HA , t DOM is in ns level. The read and write timing of the port can be simulated by programming with AT89S8252 software to configure TMC2081.

This system uses two TMC2081 chips, marked as TMC2081_0 and TMC2081_1. P3.6 of AT89S8252 is connected to R//W of TMC2081_0/1, P2.3 is connected to /CS of TMC2081_0, P2.4 is connected to /CS of TMC2081_1, P2[2:0] is connected to A[2:0] of TMC2081_0/1, and P0[7:0] is connected to D[7:0] of TMC2081_0/1 (as shown in Figure 2). The program to read and write the A channel memory of TMC2081_0 is as follows:

MC2081_0 EQU P2.3

TMC2081_1 EQU P2.4

R_NW EQU P3.6

MOV A, #00H

LCALL WADDRTMC2081_0 ;Select A channel control register

MOV A, #01H

LCALL WDATMC2081_0 ; Write 01 to A channel control register

MOV A, #00H

LCALL WADDRTMC2081_0 ;Select A channel control register

LCALL RDATMC2081_0 ;Read the contents of the A channel control register

WADDRTMC2081_0: Write control register address

SETB TMC2081_1

SETB TMC2081_0

SETB R_NW

CLR R_NW

ORL P2, #00000111B

CLR TMC2081_0

SETB R_NW

MOV P0, A

SETB TMC2081_0

RET

WDATMC2081_0: Write data to the control register

SETB TMC2081_1

SETB TMC2081_0

SETB R_NW

CLR R_NW

ANL P2, #11111101B

CLR TMC2081_0

SETB R_NW

MOV P0, A

SETB TMC2081_0

RET

RDATMC2081_0: Read control register data

SETB TMC2081_1

SETB TMC2081_0

SETB R_NW

ANL P2, #11111101B

CLR TMC2081_0

MOV A, P0

SETB TMC2081_0

RET

3.4 Key control function

There are two buttons 1 and 2. Press button 1, LED 1 lights up and displays additional digital signal 1; press button 1 again, LED 1 turns off and additional digital signal 1 does not display, and the background signal is restored. The same is true for button 2, so that two additional digital signals can be displayed at the same time. The process of displaying or not displaying the signal must be completed at the sixth falling edge of the field blanking to ensure that the process of displaying or not displaying does not affect the background signal.

Line synchronization is connected to P3.3, field blanking is connected to counter 1 (T1), buttons 1 and 2 are connected to P1.6, P1.7, P1.4 and P1.5 to send control levels to the mixer (Figure 2). In the main program of the microcontroller, a query method is used to detect whether a key is pressed. If so, enter the key processing program, first wait for a falling edge of line synchronization, then start counter T1 to count the falling edge of field blanking, and after counter T1 overflows, P1.4 or P1.5 is inverted to send a control level to the mixer. This system does not let line synchronization trigger the external interrupt 1 subroutine, but simply queries the falling edge. The actual results show that the query method is more reliable and convenient.

3.5 I 2 C Interface

I 2 C bus is a serial communication protocol proposed by Philips. Data is transmitted through the serial data line (SDA) and the serial clock line (SCL). The fastest data transmission rate is 400kbps. This system uses P1.0 and P1.1 to represent SDA and SCL, and the software simulates the I 2 C protocol.

This system makes full use of the internal resources of AT89S8252, does not require peripheral devices, and saves space. The software programming is simple and practical. This key-controlled digital video mixer based on single-chip microcomputer control has been produced by Shihui Company as KCM-D2000 Digital Key Control Mixer. Practical application shows that the mixer works stably and conveniently, and has achieved good market value.

Previous article:Design and implementation of intelligent window system based on CAN bus

Next article:Realization of Audio Processing System Based on I2C Serial Bus Using Single Chip Microcomputer

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- TL431 as a voltage regulator

- Is the product on Taobao claiming to be an energy saver genuine?

- Questions about DC Boost Circuit

- How to deal with this?

- The most touching thing in the world is the distant similarity

- Using FPGA to realize accurate time keeping when GPS is out of step

- Design of Phase Detection Broadband Frequency Measurement System Based on FPGA

- Maxim's MAX15066 high-efficiency DC-DC solution

- Frequency converter, inverter circuit

- 【RPi PICO】Soil Moisture Indicator

Design paper of dot matrix electronic display screen

Design paper of dot matrix electronic display screen The schematic diagram of the entire switch inspection unit based on AT89S8252.

The schematic diagram of the entire switch inspection unit based on AT89S8252. LT1011CN8#PBF

LT1011CN8#PBF

京公网安备 11010802033920号

京公网安备 11010802033920号