Electronic oscilloscopes are the most popular electrical signal measurement tools. Currently, the real-time bandwidth of digital storage oscilloscopes exceeds 10GHz, and the equivalent bandwidth of sampling digital oscilloscopes reaches 100GHz. Various electronic oscilloscopes are available in laboratories, workshops, and on-site for electrical signal measurement. data. According to the basic principles of electronic oscilloscopes, they can be divided into two categories: analog and digital. Since the circuit structure of analog oscilloscopes is more complex than that of digital oscilloscopes, it is not difficult to understand that all electronic oscilloscopes with a bandwidth of more than 1GHz are digital oscilloscopes. When the bandwidth exceeds 10GHz, the sampling digital oscilloscope has the advantage of having the simplest circuit structure. Except for the sampling gate that requires the highest bandwidth, the other circuits are low-speed circuits, so it is easier to obtain an equivalent bandwidth of 100GHz.

Digital storage oscilloscopes with a bandwidth of more than 1GHz and sampling oscilloscopes with an equivalent bandwidth of more than 10GHz are quite expensive per unit. Often only certain frequencies and functions are used for a specific application. In this case, it is advisable to build a user-customized digital storage or sampling oscilloscope based on the object being measured. The key components and circuits provided in this article are all new products in recent years.

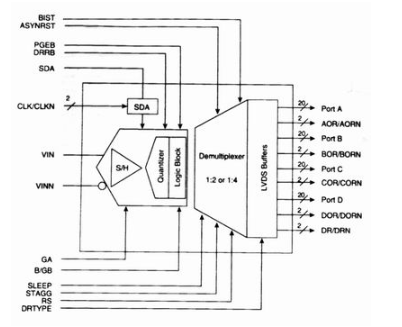

Figure 1 Structural block diagram of an ADC chip with a sampling rate of 2GS/S

Figure 2 Double-tube half-bridge sampling head circuit

Key components of digital oscilloscope

The key component of the digital storage oscilloscope, the input front-end analog-to-digital converter, is usually a high-speed integrated circuit designed by the measuring instrument company itself and is not commercially available. For example, the ADC with a bandwidth of more than 500MHz used by TeK Company in the TDS5000 and other series , jointly developed and manufactured by TeK and IBM, is very costly and can only be replaced during maintenance. It was not until this year that Atmel launched the AT84AS series of high-speed ADCs that products with a bandwidth of 1GHz, a sampling rate of 2GS/S, and a resolution of 10 bits were available. Now, electronic application engineers can purchase high-speed and high-precision ADCs to build high-frequency circuits such as data acquisition systems, digital storage oscilloscopes, automatic test systems, and direct RF converters. The AT84AS series supplied by Atmel currently has two models: AT84AS003 and AT84AS004. The former has a sampling rate of 1.5GS/S and the latter has a sampling rate of 2GS/S. The two are fully compatible. The main features of AT84AS004 are:

·Highest sampling rate-2GS/S

·Highest resolution - 10 bits

·Analog input voltage and impedance-500mv, 100Ω (differential), 50Ω (single-ended);

·Analog input bandwidth-3.3GHz

·1GHz high frequency characteristics—7.8 effective digits, signal-to-noise ratio 51dB, clutter-free dynamic range -55dB,

·Adjustment functions - ADC gain, sampling delay, valid data output, over-range indication output, 1:4 multiplex signal output.

·Power supply voltage—-5V, -2.2V, 3.3V, 2.5Vp, power dissipation 6.5W

·Packaging—EBGA317, 25×35mm

·Operating temperature -0℃~90℃ (civilian grade) -20℃~110℃ (industrial grade)

The structural block diagram of the AT84AS004 chip is shown in Figure 1. It can be seen from Figure 1 that the input signal Vin is sent to the quantizer and logic circuit through the sample and hold circuit S/H. At the clock input CLR, the sampling delay adjusts SDA and the pattern generator effective bit. The A/D conversion process is realized under the action of PGEB and reset pulse DRRB. The obtained A/D data output is amplified by the demultiplexer DMUX and the low-voltage differential buffer stage LVDS to form 4 output ports A, B, C, and D. The 4 groups of output 10-bit digital signals are used for memory, DSP, etc. Data processing usage. The chip's adjustment signals also include built-in self-test BIST, asynchronous reset ASYNRST, gain adjustment GA, binary and grayscale code selection B/GB, sleep state SLEEP, etc.

The AT84S004 chip is the ADC with the highest frequency index currently on the market. The first is that the sampling rate reaches 2GS/S and the analog input bandwidth is 3.3GHz. According to the sampling principle, ΔF ≤ Fs/2 means that the real-time bandwidth should be less than/equal to the sampling rate Fs. The chip's Fs=2GS/s, and △F=1GHz is obtained, that is, the first Nyquist zone is below 1GHz, and the second Nyquist zone extends to 2GHz. To avoid waveform confusion, digital storage oscilloscopes only use the first Nyquist zone. However, in dual-band communication applications, the second Nyquist zone can be entered because a wider input bandwidth is required. Secondly, the effective number of bits at 1GHz is 7.8 bits instead of 10 bits. Due to the increase in clock frequency and unstable voltage comparator level, the resolution at high frequencies will decrease, from 10 bits to 7.8 bits. The resolution of most commercially available digital storage oscilloscopes is 8 bits. At high frequencies it will be lower than 7 bits. In addition, the chip provides 1:2 and 1:4 multiplex digital output, which is very beneficial for back-end data processing. Flash memory and DSP with lower clocks can be used to reduce circuit costs.

Atmel's AT84AS series TDC is still under development, and the clock frequency of the CMOS chip can reach 5GHz, indicating that the sampling rate of this series has the potential to increase. Atmel has launched two ADCs, 1.5GS/S and 2GS/S, this year. Maxim's MAX108 is an ADC with 8-bit resolution and 1.5GS/S, which is also suitable for digital storage oscilloscopes.

Key components of sampling oscilloscope

The key component of the sampling oscilloscope is the sampling head, which in principle is not a digital/analog conversion process but a switching process. If the switching pulse width is represented by τ and the equivalent bandwidth is represented by ΔF, then ΔF=a1/τ is obtained, where α is a constant related to the switching pulse waveform. For example, when τ=0, ΔF =∞, that is, when the switching pulse width tends to zero, the equivalent bandwidth tends to infinity. It is generally assumed that the switching pulse is a bell-shaped function. At this time, ΔF =0.35/τ can be taken as an estimate. When τ=3.5ps, ΔF=100 GHz is obtained.

The sampling gate circuit can be a bridge circuit, usually a double-tube half-bridge switch circuit as shown in Figure 2. When the input +LO and -LO driving pulses are added to the reverse-biased fast switching diode pair, the +L0 and -L0 driving pulses are short-circuited by the 2PS microstrip line respectively, generating a 1PS level switching pulse and affecting the measured signal RF sampling. The instantaneous charge of the signal sample obtained by sampling is maintained on the Chold capacitor pair, and the sampling charge is processed and the sample is reconstructed in slow time, that is, the display process of sequential sampling is completed. It can be seen that after the sampling oscilloscope realizes high-frequency and high-speed switching transformation in the sampling gate, the back-end signal processing can be reconstructed at low frequency and low speed. If the backend uses digital processing, it is a sampling digital oscilloscope. If analog processing is used, it is an (analog) sampling oscilloscope.

There are not many circuit components in the sampling gate. The measuring instrument company made the microwave circuit on the ceramic sheet and sealed it in the metal shell. The input RF signal and the sampling pulse are connected by a small coaxial connector, which is similar to the ADC chip of the digital storage oscilloscope. The sampling There are no commercially available high-frequency, high-speed sampling heads for oscilloscopes. The situation has changed a lot in recent years. PSPL (Picosecond Pulse Laboratory) Company supplies sampling heads with bandwidths up to 100GHz, making it much easier for measurement engineers to build sampling oscilloscopes. , also promoted the development of sampling technology. Figure 2 is actually PSPL’s through-type 100GHz sampling head. The sampling head has the following characteristics:

·Sampling aperture-3ps~35ps (fixed during design)

·Aperture jitter—<1ps (RMS),

·RF bandwidth—up to 100GHz,

·RF input dynamic range—2Vp-p,

·RF impedance—50Ω, SMA~1mm coaxial connector available,

·Sampling rate—》10GS/S

·Sampling efficiency—60%

It can be seen from the above indicators that the sampling head meets the measurement of equivalent bandwidth of 10GHz~100GHz by adjusting the width of the sampling pulse, that is, the sampling aperture. Changing the length of the microstrip line in Figure 2 is the most common method. PSPL here uses a simpler and more flexible high-speed reverse step diode to replace the microstrip line to form a nonlinear short-circuit transmission line to achieve continuously adjustable sampling pulse width. Very fast rising edge. The sampling rate reaching 10GS/S is also an indicator that previous sampling heads have not had. The traditional circuit uses an avalanche transistor to generate a pulse at the step edge, and then uses a step recovery diode to shape it to obtain a 10PS level sampling pulse. The maximum operating frequency of this circuit is limited by the avalanche transistor entering the saturation zone, and it can only operate at a repetition frequency below 1MHz. PSPL uses a cascaded non-saturated amplifier circuit to shape the square wave pulse to obtain a high repetition frequency step pulse, and the sampling rate is increased from 1GS/S to 10GS/S. Therefore, PSPL's 100GHz sampling head can not only build a sampling oscilloscope with an equivalent bandwidth <100, but also be equivalent to a real-time digital oscilloscope with a sampling rate of 10GS/S.

Previous article:From time domain to frequency domain-see the world from a different perspective

Next article:Digital oscilloscope structure principle Digital oscilloscope internal structure diagram

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 12 must-know details about using an oscilloscope

- Sensirion SEK-SVM40 Review Summary

- [Pingtou Ge RVB2601 creative application development] Weather broadcaster based on Pingtou Ge RVB2601

- How to replace STM32 with GD32?

- [Homemade] DS-T10 Portable Smart Soldering Iron

- Award-winning live broadcast: Unlocking the black technology of automotive electronics and creating a new realm of future driving

- Frequently Asked Questions about Lingdongwei MM32F103 MCU

- The problem of increasing the driving capability of the oscillation circuit

- Antenna Design Solutions for Next Generation Mobile Devices

- Chapter 3 Using external interrupt EXTI to read keystrokes

Multisim Circuit System Design and Simulation Tutorial

Multisim Circuit System Design and Simulation Tutorial

京公网安备 11010802033920号

京公网安备 11010802033920号