Engineers engaged in motor control and power supply design often encounter the need to measure motor phase current and inductor current, so have you ever encountered the trouble of not having a current clamp at hand? I opened Taobao and thought about buying a current clamp, but I found that the higher-precision ones were very expensive, and the cheaper current clamps were not very accurate. what can we do about it?

The editor is short of money and since I can’t afford it, I’ll make one myself! Decided to DIY a high-precision oscilloscope current clamp costing less than 20 yuan to meet daily use needs.

First, let’s take a look at today’s protagonist, ACS712, which is a current sensor based on the Hall effect and can be used for phase current detection in motor control. It converts current signals into voltage signals. This series of Hall current sensor chips has three different current levels. This article chooses the measurement range ±20A and the accuracy of 100mV/A.

The internal block diagram of the ACS712 chip is shown in the figure above. When the current flows from IP+ to IP-, the current is positive; when the current flows from IP- to IP+, the current is negative. In order to support positive and negative current detection, there is a 2.5V DC bias inside the chip, so that the output voltage Vout is always a positive voltage. The calculation formula Vout= Ip*100mv/A+2.5V, so the Vout output is 2.5V in static state, corresponding to the current is 0A; when Vout outputs 4.5V, the corresponding current is 20A; when Vout outputs 0.5V, the corresponding current is -20A. Each current value uniquely corresponds to a voltage value.

It is recommended to connect an external capacitor to pin 6 and form a low-pass filter with the internal Rf=1.7kΩ of the chip. The cut-off frequency of the filter

, so the filter bandwidth can be set by selecting the capacitor value, 1nF is recommended.

According to the above analysis, the output signal voltage Vout from ACS712 ranges from 0.5V to 4.5V, which is always positive. If it is displayed directly on an oscilloscope, the positive and negative current cannot be observed intuitively. In order to maintain the existing current clamp usage habits, it is hoped that when the input current is 0, the corresponding output voltage is also 0V.

In order to restore the original measured current signal as much as possible on the oscilloscope and achieve the same effect as the actual current clamp test, the output signal of the ACS712 needs to be processed. The program design will be introduced in detail below.

Hardware design block diagram

The hardware circuit is divided into two parts: power circuit and signal conditioning circuit.

In order to realize the display of positive and negative current, the operational amplifier in the circuit needs to be powered by dual power supplies. The board is powered by a 9V instrument battery, uses LM7805 to stabilize the voltage to +5V, and then uses SGM3204 to stabilize the voltage to -5V.

The signal conditioning circuit processes the output signal of the ACS712. It first subtracts the +2.5V DC bias voltage, and then uses a non-directional amplification circuit to process the output. A low-pass filter is also used in the circuit to filter out the device noise of the ACS712.

signal conditioning circuit

The subtraction circuit is used to subtract the 2.5V DC bias voltage output by the ACS712, so that the collected positive and negative currents corresponding to the output voltage are also positive and negative. The circuit principle is shown in the figure below:

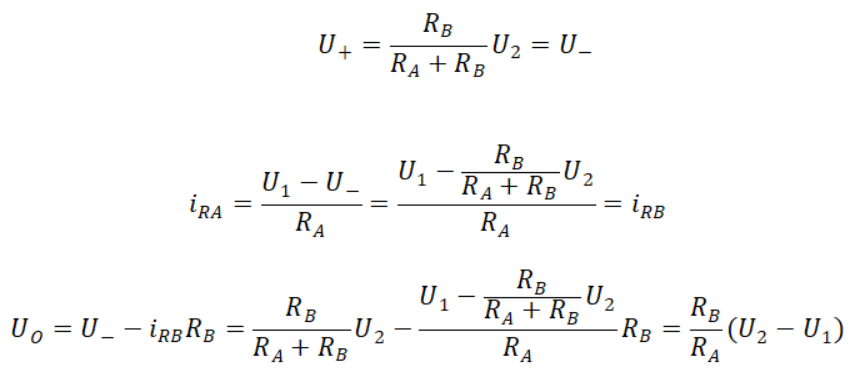

Its output voltage

The derivation process is (this circuit satisfies virtual short-term interruption):

The actual circuit is shown below:

It can be seen from the differential amplifier circuit gain calculation formula that the gain of this circuit on the input signal is 1. The non-inverting input end of the op amp (left end of R9) is connected to the ACS712 signal output, and the inverting input end of the op amp (the left end of R12) is connected to the 2.5V DC reference voltage, which just subtracts the 2.5V DC bias in the ACS712. According to the above analysis, the output Vo of the op amp = Ip*100mv/A, which just solves the output DC bias voltage problem of ACS712 and achieves 0A corresponding to 0V.

There are many methods to obtain the 2.5V voltage reference, such as using TL431, special reference source chip, resistor voltage divider, etc. Here I used the simplest method, using resistor voltage division to get 2.5V, and then using an operational amplifier to build a voltage follower to reduce the signal output impedance and improve the 2.5V voltage accuracy. The circuit is as shown below (RP1 in the circuit is not soldered ):

Power circuit design

In order to be compatible with traditional current clamp usage habits, the entire circuit is powered by a 9V instrument battery. Use a diode on the input for reverse polarity protection.

From the above analysis, it can be seen that the op amp needs to be powered by dual power supplies, using LM7805 to obtain a stable 5V voltage, and then using the charge pump chip SGM3204 to obtain a -5V power supply.

LM7805 is a conventional LDO voltage reduction solution. The implementation principle will not be discussed here. Let’s take a look at how SGM3204 converts +5V voltage into -5V voltage.

SGM3204 uses charge pump technology, which cleverly uses the characteristic that the voltage at both ends of the capacitor cannot change suddenly. Through high-frequency switching of the capacitor charge and discharge circuit, the power supply output voltage is flipped to negative voltage.

The picture below is taken from the SGM3204 data sheet. When S1 and S3 are closed and S2 and S4 are open, the capacitor Cfly is charged to Vin, and the voltage across the capacitor is high on the left and low on the right. When S1 and S3 are disconnected and S2 and S4 are closed, the left end of the capacitor Cfly is grounded. Since the capacitor voltage cannot change suddenly, the voltage at both ends of the capacitor is still high on the left and low on the right. The voltage at the right end of the capacitor, that is, the output voltage Vout, becomes a negative voltage with a magnitude of -Vin . (Ignore the voltage drop of each switch tube)

Simulate the above schematic diagram in Tina. First, VG1 is set to 5V square wave output and the frequency is set to 1Mhz.

The high and low level switching of VG1 simulates the switches S1 and S2 in the schematic diagram of the SGM3204 manual. When the level is high (S1 is on, S2 is off), when the level is low (S1 is off, S2 is on). The diode simulates the switching tubes S3 and S4. According to the unidirectional conductivity of the diode, it meets the switching logic of the charge pump.

It can be seen from the simulation waveform that after 10us, the output voltage VF1 gradually stabilizes at -3.37V.

After 1000us, the output voltage VF1 finally stabilized at -4.14V. Because the diode has a forward conduction voltage drop, the output voltage loses 0.86V. These are the principles of the charge pump negative voltage circuit. Let's take a look at the selection of key components in the use of SGM3204.

The recommended circuit of SGM3204 is relatively simple and can be used normally with three external capacitors. They are the input bypass capacitor Cin, the "pumping" capacitor Cfly, and the output capacitor Cout.

The selection of the "pumping" capacitor Cfly and the output capacitor Cout is crucial. Together they determine the output impedance and output voltage ripple of the charge pump power supply.

The output impedance of the charge pump is calculated from the following formula. The impedance of Cfly during operation is inversely proportional to the product of its capacitance size and switching frequency. Rs witch is the on-resistance of the internal switch, and ESR is the equivalent series resistance of the capacitor.

The size of the charge pump's output impedance will directly affect the output voltage. When the output current increases, the output voltage will tend to decrease due to the existence of the output resistance.

Therefore, when selecting capacitors, you need to choose low-ESR chip ceramic capacitors. You can also reduce the ESR of the capacitor by connecting multiple small capacitors in parallel. At the same time, appropriately increasing the Cfly capacitance value according to the following formula can also reduce the charge pump output impedance, but please remember to increase it appropriately.

The output capacitor Cout directly affects the ripple of the output voltage. The peak-to-peak value can be calculated according to the following formula

It can be seen from the formula that if the output capacitor is made relatively large, a very small output ripple voltage can be achieved.

This is a theoretical calculation result. In practice, it is limited by the current flow capacity of the internal switch tube of SGM3204. If Cout is selected too large, a surge current will be generated in the charge and discharge circuit due to the relatively small internal resistance, which may damage the chip in severe cases.

As shown in the figure below, when adding 5 ohm internal resistance and using a 3.3uf capacitor, there is a surge current of 800ma during charging and discharging of the capacitor.

The "pumping" capacitor Cfly and the output capacitor Cout should remain equal in size, because when the S2 and S4 switches are closed, Cfly and Cout are a process of sharing (average) charge. When the two capacities are equal, they can be faster. Reach output stable voltage.

In the design, the capacity values of the "pumping" capacitor Cfly and the output capacitor Cout adopt the 3.3uf recommended by the manual. Use this parameter to test the ripple effect, the ripple is less than 10mv:

Interface circuit design

Commonly used oscilloscope probes use BNC interfaces, in order to minimize the attenuation of the signal between the PCB board and the oscilloscope, and at the same time ensure good interface matching. In the design, an SMA RF socket is used, and then an SMA to BNC RF cable is used to connect to the oscilloscope. SMA is gold-plated at the connector, and uses shielded connecting wires to shield against interference and ensure the stability of the transmission signal.

Previous article:Tektronix DPO7104 Digital Phosphor Oscilloscope

Next article:Technical parameters of Puyuan digital oscilloscope MSO8104

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- [ESP32-S2-Kaluga-1 Review] 5. Use LGVL to create a low-level interface?

- Kill TPS54340

- Why is the voltage ringing spike of MOSFET different in boost and buck mode?

- The circuit for discharging the PFC output capacitor is shown in Figure 2.

- Basic syntax of Verilog HDL

- Found a method to import Altium Designer into SIwave

- Thanks to okhxyyo for searching and fish001 for sharing

- Please advise, is it easy to pass the postgraduate examination and graduate, and how useful is the degree certificate?

- About the LAUNCHXL-F28379D Development Kit

- Limited time 1 yuan patch! Save up to 10,000 yuan!

Monocular semantic map localization for autonomous vehicles

Monocular semantic map localization for autonomous vehicles CVPR 2023 Paper Summary: Vision Applications and Systems

CVPR 2023 Paper Summary: Vision Applications and Systems

京公网安备 11010802033920号

京公网安备 11010802033920号