Home >

Detection Circuits >Instrumentation > Railway-specific 150MHz ultra-short wave interference direction finder circuit

Railway-specific 150MHz ultra-short wave interference direction finder circuit

Source: InternetPublisher:方世玉223 Updated: 2015/05/15

Part of the circuit of the 150MHz ultra-short wave interference direction finder developed and designed specifically for railways. The frequency output by the voltage-controlled oscillator in the FM receiver MC3363 is pre-divided by the dual-mode prescaler MC12017, and then output to the programmable parallel input phase-locked loop MC145152. , the microcontroller AT89C51 programs the MC145152 through the I/O port to change the initial counting value of its counter, thereby changing the frequency division ratio. The error signals φV and φr output by the dual output terminals of the phase detector are input to a first-level dual circuit composed of LM358. An active low-pass filter with terminal input, in which R10, R18, R12, C16, etc. constitute the RC low-pass link of the active filter input circuit, while R11 and C17 constitute the high feedback link of the active filter. The peak detector composed of D1 and C14, R9, and C15 networks further smoothes the error voltage output by the active filter, and then directly controls the voltage-controlled oscillator in MC3363, forming a complete numerically controlled phase-locked loop. The microcontroller receives the manually adjusted and set values, and presets the initial counter value of MC145152 differently to lock different frequencies and achieve the purpose of changing signals at different frequencies. After the signal corresponding to the frequency point is sent to the microcontroller through A/D, it is then input to the character display to display the signal field.

MC145152 frequency synthesizer and its application 1. Overview

MC145152 frequency synthesizer and its application 1. Overview

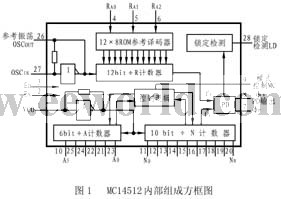

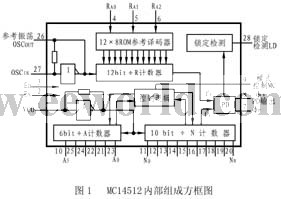

MC145152 is a large-scale integrated circuit produced by MOTOROLA. It is a half-line code The input mode is set and the dual-mode CMOS-LSI phase-locked loop frequency synthesizer is programmed by 14 parallel input data. Its internal block diagram is shown in Figure 1. The chip contains a reference frequency oscillator, user-selectable reference divider (12×8ROM reference decoder and 12bit÷R counter), double-ended output phase detector, control logic, 10-bit programmable 10-bit ÷N counter, 6-bit programmable 6bit÷A counter and lock detection parts. Among them, 10bit÷N counter, 6bit÷A counter, analog control logic and external dual-mode prescaler form the pulse swallowing program frequency divider. The total frequency division ratio of the pulse swallowing program frequency divider is: D=VN+A. 2. Pin arrangement and function

MC145152 is a large-scale integrated circuit produced by MOTOROLA. It is a half-line code The input mode is set and the dual-mode CMOS-LSI phase-locked loop frequency synthesizer is programmed by 14 parallel input data. Its internal block diagram is shown in Figure 1. The chip contains a reference frequency oscillator, user-selectable reference divider (12×8ROM reference decoder and 12bit÷R counter), double-ended output phase detector, control logic, 10-bit programmable 10-bit ÷N counter, 6-bit programmable 6bit÷A counter and lock detection parts. Among them, 10bit÷N counter, 6bit÷A counter, analog control logic and external dual-mode prescaler form the pulse swallowing program frequency divider. The total frequency division ratio of the pulse swallowing program frequency divider is: D=VN+A. 2. Pin arrangement and function

The pin arrangement of MC145152 is shown in Figure 2. It is packaged in a 28-pin DIP, and the functions of each pin are as follows:

The pin arrangement of MC145152 is shown in Figure 2. It is packaged in a 28-pin DIP, and the functions of each pin are as follows:

Pins 4, 5, and 6 (RA0, RA1, RA2) are the reference address code input terminals, used to select the frequency division ratio of the reference divider. Programming via 12×8ROM reference decoder and 12bit÷R counter. There are 8 choices for the frequency division ratio. The relationship between the reference address code and the frequency division ratio is shown in Table 1. Pins 26 and 27 (OSCIN, OSCOUT) are the reference oscillator terminals. When the two pins are connected to a parallel resonant crystal, a reference frequency oscillator is formed. However, a frequency setting capacitor (usually around 15pF) should be connected between OSCIN to ground and OSCOUT to ground. OSCIN can also be used as an input terminal for external reference signals. Pin 1 (VCO) is the input signal terminal. The input signal is AC coupled to this pin. The input signal frequency should be less than 30MHz. Pins 10 and 21~25 (A5~A0) are the frequency dividing terminals of the 6bit÷A counter. The preset number determines the number of ÷V/(V+1) dual-mode preamplifiers

Pins 4, 5, and 6 (RA0, RA1, RA2) are the reference address code input terminals, used to select the frequency division ratio of the reference divider. Programming via 12×8ROM reference decoder and 12bit÷R counter. There are 8 choices for the frequency division ratio. The relationship between the reference address code and the frequency division ratio is shown in Table 1. Pins 26 and 27 (OSCIN, OSCOUT) are the reference oscillator terminals. When the two pins are connected to a parallel resonant crystal, a reference frequency oscillator is formed. However, a frequency setting capacitor (usually around 15pF) should be connected between OSCIN to ground and OSCOUT to ground. OSCIN can also be used as an input terminal for external reference signals. Pin 1 (VCO) is the input signal terminal. The input signal is AC coupled to this pin. The input signal frequency should be less than 30MHz. Pins 10 and 21~25 (A5~A0) are the frequency dividing terminals of the 6bit÷A counter. The preset number determines the number of ÷V/(V+1) dual-mode preamplifiers

. Pins 11~20 (N9~N0) are the frequency dividing terminals of the 10bit÷N counter. Pins 7 and 8 (φV, φr) are the dual output terminals of the phase detector, used to output loop error signals. If fV>fr or the phase of fV leads fr, φV becomes low level and φr remains high; if fV

. Pins 11~20 (N9~N0) are the frequency dividing terminals of the 10bit÷N counter. Pins 7 and 8 (φV, φr) are the dual output terminals of the phase detector, used to output loop error signals. If fV>fr or the phase of fV leads fr, φV becomes low level and φr remains high; if fV

MC145152 frequency synthesizer and its application 1. Overview

MC145152 frequency synthesizer and its application 1. Overview

MC145152 is a large-scale integrated circuit produced by MOTOROLA. It is a half-line code The input mode is set and the dual-mode CMOS-LSI phase-locked loop frequency synthesizer is programmed by 14 parallel input data. Its internal block diagram is shown in Figure 1. The chip contains a reference frequency oscillator, user-selectable reference divider (12×8ROM reference decoder and 12bit÷R counter), double-ended output phase detector, control logic, 10-bit programmable 10-bit ÷N counter, 6-bit programmable 6bit÷A counter and lock detection parts. Among them, 10bit÷N counter, 6bit÷A counter, analog control logic and external dual-mode prescaler form the pulse swallowing program frequency divider. The total frequency division ratio of the pulse swallowing program frequency divider is: D=VN+A. 2. Pin arrangement and function

MC145152 is a large-scale integrated circuit produced by MOTOROLA. It is a half-line code The input mode is set and the dual-mode CMOS-LSI phase-locked loop frequency synthesizer is programmed by 14 parallel input data. Its internal block diagram is shown in Figure 1. The chip contains a reference frequency oscillator, user-selectable reference divider (12×8ROM reference decoder and 12bit÷R counter), double-ended output phase detector, control logic, 10-bit programmable 10-bit ÷N counter, 6-bit programmable 6bit÷A counter and lock detection parts. Among them, 10bit÷N counter, 6bit÷A counter, analog control logic and external dual-mode prescaler form the pulse swallowing program frequency divider. The total frequency division ratio of the pulse swallowing program frequency divider is: D=VN+A. 2. Pin arrangement and function

The pin arrangement of MC145152 is shown in Figure 2. It is packaged in a 28-pin DIP, and the functions of each pin are as follows:

The pin arrangement of MC145152 is shown in Figure 2. It is packaged in a 28-pin DIP, and the functions of each pin are as follows:

Pins 4, 5, and 6 (RA0, RA1, RA2) are the reference address code input terminals, used to select the frequency division ratio of the reference divider. Programming via 12×8ROM reference decoder and 12bit÷R counter. There are 8 choices for the frequency division ratio. The relationship between the reference address code and the frequency division ratio is shown in Table 1. Pins 26 and 27 (OSCIN, OSCOUT) are the reference oscillator terminals. When the two pins are connected to a parallel resonant crystal, a reference frequency oscillator is formed. However, a frequency setting capacitor (usually around 15pF) should be connected between OSCIN to ground and OSCOUT to ground. OSCIN can also be used as an input terminal for external reference signals. Pin 1 (VCO) is the input signal terminal. The input signal is AC coupled to this pin. The input signal frequency should be less than 30MHz. Pins 10 and 21~25 (A5~A0) are the frequency dividing terminals of the 6bit÷A counter. The preset number determines the number of ÷V/(V+1) dual-mode preamplifiers

Pins 4, 5, and 6 (RA0, RA1, RA2) are the reference address code input terminals, used to select the frequency division ratio of the reference divider. Programming via 12×8ROM reference decoder and 12bit÷R counter. There are 8 choices for the frequency division ratio. The relationship between the reference address code and the frequency division ratio is shown in Table 1. Pins 26 and 27 (OSCIN, OSCOUT) are the reference oscillator terminals. When the two pins are connected to a parallel resonant crystal, a reference frequency oscillator is formed. However, a frequency setting capacitor (usually around 15pF) should be connected between OSCIN to ground and OSCOUT to ground. OSCIN can also be used as an input terminal for external reference signals. Pin 1 (VCO) is the input signal terminal. The input signal is AC coupled to this pin. The input signal frequency should be less than 30MHz. Pins 10 and 21~25 (A5~A0) are the frequency dividing terminals of the 6bit÷A counter. The preset number determines the number of ÷V/(V+1) dual-mode preamplifiers

. Pins 11~20 (N9~N0) are the frequency dividing terminals of the 10bit÷N counter. Pins 7 and 8 (φV, φr) are the dual output terminals of the phase detector, used to output loop error signals. If fV>fr or the phase of fV leads fr, φV becomes low level and φr remains high; if fV

. Pins 11~20 (N9~N0) are the frequency dividing terminals of the 10bit÷N counter. Pins 7 and 8 (φV, φr) are the dual output terminals of the phase detector, used to output loop error signals. If fV>fr or the phase of fV leads fr, φV becomes low level and φr remains high; if fVLatest Detection Circuits Circuits

- Make a Simple Darkness Detector Circuit

- Convenient and fast power line break detection circuit

- Digital electronic thermometer using semiconductor diode as temperature sensor

- LM3914 makes car battery detector

- 1.5V and 9V battery tester circuit diagram

- AC equivalent amplifier circuit

- High-speed gain programmable amplifier circuit

- High resistance DC differential amplifier circuit

- Temperature voltage conversion circuit

- The three-phase three-wire active energy meter is connected to the circuit through the current transformer (1)

Popular Circuits

- LED lighting display detection circuit with overload protection

- Towel machine fault detection circuit

- Bus door status detection circuit

- Combustible gas concentration detection circuit

- Detect the major point waveforms of the circuit

- Cable automatic detection circuit

- Cordless telephone ring current detection circuit

- Human body detection circuit for infrared sensor

- Portable CO detection circuit using dual-electrode sensor

- Revolution detection circuit

京公网安备 11010802033920号

京公网安备 11010802033920号