Abstract: This paper analyzes various traditional interconnection methods of multiple DSPs and proposes to use the Serial RapidIO protocol, a switch-based, point-to-point interconnection method, as an interconnection solution in baseband data processing, which can reduce costs and provide low-latency bidirectional communication under high bandwidth. Then, combined with base station baseband processing, this solution has great flexibility, and finally summarizes the benefits of using this interconnection solution.

At present, in communication systems, such as VoIP gateways and wireless base stations, voice and data are increasing rapidly, and the processing capacity of the system must also be greatly increased. Therefore, a single DSP can no longer meet the increasing demand. It is necessary to interconnect multiple DSPs into a DSP cluster to increase the faster processing capacity of more data. There are many kinds of DSP interconnection, and different DSP interconnections can be used in different applications. For example, the bus-based multi-DSP structure is complex, and the bus bandwidth is reduced because of the shared bus, which reduces the overall efficiency of the system, and the limitation of the bus bottleneck will be highlighted; through the HPI interface-it can provide interconnection between DSPs, but the data transmission rate is limited. Data transmission sometimes becomes a bottleneck for improving the processing capacity of the system, resulting in a reduction in the overall efficiency of the system; multi-channel buffered serial port MCBSP-data transmission bandwidth is limited, and they are not suitable for high-speed data transmission between multiple DSPs. DSP clusters need to be interconnected in a special way to support higher bandwidth and low-latency two-wire communication at the same time. The multi-DSP interconnection solution can be implemented through a dedicated interconnection chip, so that the connection will not be complicated and has the characteristics of flexibility and high-speed transmission. In wireless base stations, if the RapidIO protocol is used for DSP interconnection, the computing efficiency can be greatly improved. Moreover, chip manufacturers have already produced chips that support the Serial RapidIO interface, making high-speed interconnection between DSPs possible.

1. System Introduction

1.1 Serial RapidIO

The RapidIO Business Alliance proposed the RapidIO protocol for multi-processor interconnection in 2001. The RapidIO protocol is a point-to-point packet switching protocol with a three-layer structure of physical layer, transport layer and logical layer. The logical layer defines all packet formats for transactions of RapidIO nodes: the transport layer provides routing and addressing functions for RapidIO data packets; the physical layer provides electrical characteristics of the device interface. In addition, the protocol also provides flow control, error control and other functions. For long-distance transmission with fewer connections and backplane transmission, since the RapidIO physical layer uses Lvds transmission and high-speed serial transceiver technology, it supports up to 10-Gbps data throughput in each direction, and can be used in image and signal processing, high-bandwidth memory interface and other fields.

1.2 DSPs are interconnected via Serial RapidIO

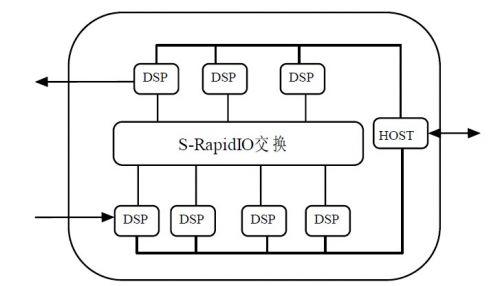

If the interconnection of the DSP cluster uses the Serial RapidIO protocol, the throughput can be greatly improved, as shown in Figure 1:

Figure 1 A preliminary interconnection scheme

It can be seen that several DSPs are interconnected in this way, using two DSPs to collect unprocessed data from the outside and send out processed data. The serial RapidIO protocol is used inside several DSPs, and the data runs at high speed between several DSPs. It is precisely because of the point-to-point transmission characteristics of RapidIO that high-speed transmission can be achieved. In addition, some functions of these DSPs can be controlled through an external host host. For example, in some occasions, only a certain DSP can be run for special operations, and other DSPs are in a non-working state. This kind of DSP interconnection using serial RapidIO has many advantages:

1. RapidIO protocol is divided into three layers, and all DSPs can centrally process the code rate and symbol rate.

2. It has an upgradeable interleaved lookup table that can balance the workload of several DSPs.

3. This point-to-point switch interconnection can meet higher and more complex requirements, such as multi-user detection, etc.

4. Four priority settings in the protocol allow high-priority communications.

5. For data streams in RapidIO, the sixth data type can be selected, allowing data transmission to have a smaller packet header.

1.3 Baseband part of wireless transmission system

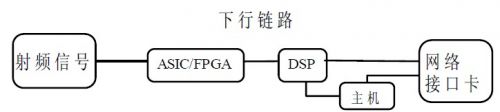

In wireless transmission, the simulated user data is converted by the RF module and sent to the baseband board of the base station for reception. A series of operation rules are run to perform modulation and demodulation to analyze the user data. The baseband subsystem completes the functions of channel despreading and demodulation, coding and decoding, and spread spectrum modulation. The baseband subsystem demodulates the uplink baseband data, including correlation, channel estimation, frequency tracking and RAKE merging, and then passes it to the transmission subsystem after decoding and FP processing. In the downlink, the baseband subsystem receives the FP packet from the transmission subsystem, completes the encoding according to the requirements, including TB block CRC check and code block segmentation, channel coding, rate matching, interleaving, transmission channel multiplexing and physical channel mapping, and sends the downlink data to the intermediate frequency subsystem. Among them, cross-correlation, channel estimation and multi-user detection are usually implemented with ASIC and FPGA, and Viterbi decoding and turbo decoding are usually implemented with DSP. As shown in Figure 2:

Figure 2 Simplified block diagram of base station baseband processing board

Traditional ASIC/FPGA processors do not have peer-to-peer network requirements, and have fixed allocations for voice and data, resulting in low processing efficiency. Therefore, DSP can be considered for implementation, but a single DSP has only one core, and its processing power is very limited, and the speed of processing data is not as fast as FPGA. If multiple cores collaborate for parallel computing, the processing power of DSP can be increased exponentially, so multiple DSPs can be interconnected. A DSP cluster composed of multiple DSPs interconnected by high-speed protocols can flexibly implement multiple functions. Through software programming, they can flexibly adapt to more complex requirements, and make peer-to-peer network communication possible, with higher throughput.

Since only DSPs are operating in this module, load balancing is required. For the DSP cluster in the processing chain, different algorithm modules need to be assigned to each DSP. Because higher data rates and more complex multi-user operations are required for channel estimation and detection, multiple DSPs need to be load balanced for these operations to achieve larger algorithm modules. For example, the same algorithm can be given to each DSP, or each DSP can be made an independent algorithm module. These are very flexible.

2. Specific implementation of the system

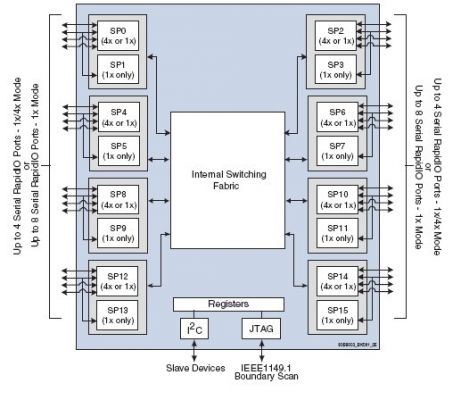

The method of implementing communication between DSPs through the RapidIO protocol can currently be implemented through FPGA. FPGA, as a local interconnection network coprocessor of DSP nodes, adopts a layered structure, including DSP interface layer, RapidIO logical layer, transport layer and physical layer [4]. DSP is connected to FPGA through external memory interface (EMIF). However, this method requires relatively complex interconnection inside FPGA. At present, TUNDRA has launched a special serial RapidIO chip - TSI568A.

Figure 3 The internal structure of Tsi568a. [page]

Tsi568A is the most advanced serial RapidIO switch in the industry, supporting a total bandwidth of up to 80GB per second. Its high flexibility can meet the bandwidth requirements of multiple I/O devices, and each port can be configured in 4x mode or 1x mode, which can provide interfaces for multiple DSP connections. Tsi568A also supports RapidFabric expansion, including data stream packet switching for the purpose of interactive work and encapsulation. And Tsi568a supports hot-swappable I/O devices. At the same time, TI's TMS320C6455 series DSP also integrates a serial RapidIO interface, so that seamless serial RapidIO communication can be achieved between DSP clusters.

Fig. 4 Interconnection implementation.

As shown in Figure 3, the baseband processing at the receiving end. Autocorrelation and multipath estimation are completed by DSP1 and DSP2, channel estimation and multi-user detection are completed by DSP3 and DSP5, QPSK and MRC are also processed by DSP5, and turbo decoding and viterbi decoding are completed by DSP7. It can also be seen that DSP4 and DSP6 are not used. At this time, they can enter the power down mode, and it can be decided whether to use a certain DSP according to needs.

In addition, the above figure is only the baseband processing of the receiving end. Different or the same functions are assigned to each DSP, so that the DSP processing board can also be used in the system's multi-antenna receiving board, multi-antenna transmitting board, and baseband receiving processing board. Because of the equal relationship, the use of appropriate upgrades can flexibly implement the sending and receiving functions in one board. In addition to the functional differences, different boards require different processing capabilities, and different DSPs can be selected to adapt. If the processing capability requirement is not high, you can choose 6455-720 or 6455-850 with a lower operating frequency; if the processing capability requirement is relatively high, you can choose 6455-1000 with the highest operating frequency. In this module processing mechanism, each DSP performs this series of channel processing functions. At certain times, several DSPs can enter the power down mode, and TSI568a can also interrupt unused ports to save power. When the traffic volume is high, all DSPs can be enabled to work.

With the Tsi568A series switches, you can choose flexible port configurations for each DSP through a variety of port bandwidth and frequency options. The system is based on the Serial RapidIO specification and has multiple features: SerDes, error recovery, prioritized system routing, high payload, and table-based system packet routing. Due to its extensive buffering and traffic management architecture, it can effectively prevent congestion in the line hub. Tsi568a provides chip-to-chip interconnection, so the data transmission of several DSPs is point-to-point. At the same time, Tsi568A can provide traffic aggregation by distinguishing the priorities of data packets and provide high-performance peer-to-peer communication through its own non-blocking system. Through x4 Serial RapidIO connection, it can have a higher channel density and carry higher throughput.

3. Conclusion

Flexible use of the serial rapidio protocol in the baseband processing structure of the base station can reduce complexity, make the circuit board design simpler, and implement the sending and receiving functions more flexibly in one board. In addition, multiple DSPs simultaneously perform parallel computing to enhance the baseband processing capabilities; allow more flexible field switching; make up for the shortcomings of traditional interconnection solutions, have upgradeable space, and can upgrade algorithms and data paths through software improvements.

Previous article:Design of constant current charging power supply based on DSP

Next article:Application of DSP technology based on 3G era

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- Detailed explanation of the three major weapons to eliminate EMC: capacitors/inductors/magnetic beads

- USB Association published the standard book - about USB TYPE C

- Embedded operating systems I have come into contact with - time-slice-based embedded systems, RTX, FREERTOS, RT-THREAD

- How much do you know about RF semiconductor technology in the wireless era?

- How to design the vias on the heat sink? The problem is not solved, please help me

- Design and simulation of 4PSK modulator based on VHDL.pdf

- 【EETALK】Are you interested in products like this? Tell us what kind of power supply products you want to try/review.

- Interesting positioning

- Analysis of key technologies of WiMAX system [Repost]

- Analysis of Active Precision Detection Circuit

RapidIO™ Interconnect Specification

RapidIO™ Interconnect Specification

京公网安备 11010802033920号

京公网安备 11010802033920号