2 Convolutional encoder Convolutional code is usually recorded as (n 0 ,k 0 ,m), its coding efficiency is k 0 /n 0 , and m is called the constraint length. (n 0 , k 0 , m) convolutional code can be implemented with k 0 inputs, n 0 outputs, a linear finite state shift register with input storage m and a modulo 2 addition counter circuit. The encoding method of the convolutional code is 3 operation methods: discrete convolution method; generating matrix method; polynomial product method. In addition, the encoding process of convolutional codes can also be described by state diagrams, code tree diagrams and trellis diagrams. The encoder designed in this article takes into account the implementation of the hardware circuit and chooses the polynomial product method. The convolutional encoder selected for this system is shown in Figure 1. The convolutional encoder is a (2, 1, 6) auto-orthogonal convolutional encoder.

?

?3 Large number logic decoder The decoding of convolutional codes can be divided into two categories: algebraic decoding and probabilistic decoding. The large number logic decoder is the most important decoding method for algebraic decoding. It can be used to correct both random errors and burst errors, but it requires the convolutional code to be a self-orthogonal code or an orthogonal code. The large-number logic decoder of the (2, 1, 6) system auto-orthogonal convolutional code selected in this article is shown in Figure 2.

In Figure 2, the I terminal inputs the information symbol, and the P terminal inputs the verification symbol. The decoder sends each piece of information element in the received R(D) to the encoder to find the local check element, and adds it modulo 2 to the check element received later. If the two are consistent, the obtained adjoint component si is 0, otherwise it is 1. Send the added value to the associated register for storage. After receiving 7 code segments, the error correction of the 0th code segment begins . If the output of the majority logic gate is 1 at this time, it means that the information element of the 0th code segment is incorrect. At this time, the information elements of the 0th subgroup are moved to the output of the decoder, thereby correcting them. At the same time, the error correction signal is also fed back to the syndrome register to correct the syndrome to eliminate the impact of this error on the syndrome. If the large number decision gate has no output, it means that the information element of the 0th subgroup has no error, and the information element is output directly from the encoder.

4. VHDL design of convolutional codec

. Its program structure is characterized by dividing an engineering design (or design entity) into external (ie, port) and internal (ie, function, algorithm). After defining an external port for a design entity, other designs can directly call this entity once internal development is completed. The VHDL design platform used in this design is Altera's MAX+PlusⅡ EDA software. MAX+PlusⅡ has a friendly interface and is easy to use; it supports VHDL, schematic diagrams, V language text files, and files in waveform and EDIF formats as design input; and supports any mixed design of these files; it has a gate-level simulator that can Functional simulation and timing simulation can produce accurate simulation results; support all Altera FPGA/CPLD large-scale logic devices except APEX20K, APXⅡ, Mercury, Excalibur and Stratix series. The FPGA device used in the design is Altera's FLEX series chip FLEX 10K20. The process of using MAX+PlusⅡ software for VHDL design is: (1) Use Text Editor to write VHDL programs. (2) Use Compiler to compile the VHDL program. (3) Use Waveform Editor and Simulator to simulate and verify the VHDL program. (4) Use Timing Analyzer to perform timing analysis of the chip. (5) Use Floorplan Editor to arrange the chip pin positions. (6) Use Programer to download the program to the chip FLEX10K20. In the actual development process, the above steps need to be repeated until the established VHDL design passes all tests.

4.2 Convolutional encoder VHDL top level modeling (top level) and system function simulation

4.2.1 VHDL description of each functional module and top-level modeling port of

the convolutional encoder LIBRARY IEEE;

encoder generated after compiling with MAX+PlusⅡ The graphic symbol is shown in Figure 3.

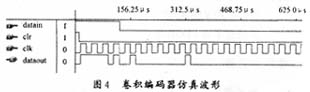

4.2.2 VHDL simulation waveform of convolutional encoder VHDL top-level modeling

?

?4.3 VHDL port description of the VHDL top-level modeling of the

convolution decoder 4.3.1 VHDL description of each functional module and top-level modeling port of the convolution

decoder LIBRARY IEEE; the decoder graphic symbol generated after compiling with MAX+PlusⅡ is as shown in the figure 5 shown. 4.3.2 VHDL simulation waveform of convolutional decoder VHDL top-level modeling The convolutional decoder VHDL simulation waveform is shown in Figure 6. Among them, the cell to be decoded datain=“11111010010000000001”, the rate is 64kP/s, and the corresponding clock is 15.625μs. The simulation results show that the decoded cell output dataout = "111 1", and the corresponding rate is 32kP/s. The actual simulation also verified the error correction situation when there are error codes in the cells to be decoded input by the convolution decoder, which is consistent with the theoretical analysis results.

?

?[ 1] Wang Xinmei, Xiao Guozhen. Error correcting codes—Principles and methods [M]. Xi'an: Xi'an University of Electronic Science and Technology Press, 2001. [

2] Chu Zhenyong, Weng Muyun. FPGA design and application [M]. Xi'an: Xi'an University of Electronic Science and Technology Press, 2002.

[3] Pan Song, Wang Guodong. VHDL Practical Tutorial [M]. Chengdu: University of Electronic Science and Technology Press, 2 000

Previous article:Research on hardware solutions for digital scanning probe microscope based on DSP

Next article:Design of radar pulse compression system based on FPGA

Recommended ReadingLatest update time:2024-11-16 21:54

- Popular Resources

- Popular amplifiers

-

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei) -

MATLAB and FPGA implementation of wireless communication

MATLAB and FPGA implementation of wireless communication -

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong)

Intelligent computing systems (Chen Yunji, Li Ling, Li Wei, Guo Qi, Du Zidong) -

Summary of non-synthesizable statements in FPGA

Summary of non-synthesizable statements in FPGA

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- MSP430G2553 Software UART and Hardware UART and Jumper Settings

- The "backplane problem" is broken down, let's see how we catch the monster

- Learn 3D visualization from scratch: Camera "sweet spot"

- Optimization of CCS for TMS320C66x

- What are the definitions of Alternate and Remap in the manual?

- Recommended "Intelligent Sensor Systems: Emerging Technologies and Their Applications", those who are interested in sensors can take a look

- diode

- 【GD32L233C-START Review】WS2812B Display Driver

- Diwen 86 box data sharing

- Avoiding ESD and EMI in mobile audio systems

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

Analysis and Implementation of MAC Protocol for Wireless Sensor Networks (by Yang Zhijun, Xie Xianjie, and Ding Hongwei)

京公网安备 11010802033920号

京公网安备 11010802033920号