|

With the development of high-speed A/D conversion technology and DSP technology, intermediate frequency digital processing technology has also been developed. IF digital processing technology is one of the important technologies to improve the performance of modern communication receivers. As the core device of IF digital processing, early A/D converters were unable to meet the high-speed digitization requirements of IF digital receivers due to limitations in speed and accuracy. This article will take the IF digital receiver of a differential frequency hopping radio based on software radio technology as an example to give a design solution for an IF digital processing module based on a new ADC device - AD6644. 1 System overall structure design

The structure of the IF digital receiving system of this solution is shown in Figure 1. Because the differential frequency hopping system is an asynchronous frequency hopping system, the synchronous circuit is omitted and the structure is simplified. The system mainly consists of three parts: RF front-end, IF pre-processing and IF digital processing. The main functions of the system are: working in the shortwave frequency band (2~30MHz), sampling signals with a frequency hopping rate of 5000 hops/s and a bandwidth of 2.56MHz at no less than 12 bits, sending them to the DSP at a suitable data rate, and then Various algorithm processing is completed by DSP. The radio frequency signal is first amplified by a 2~30MHz pre-filter amplifier circuit. In order to effectively suppress the combined frequency interference and sub-channel interference, the intermediate frequency preprocessing part of this system adopts the intermediate frequency scheme 3. After the signal is filtered and amplified, it is down-converted twice to obtain a low-IF signal of 5.12MHz. After the signal passes through the band-pass filter amplification circuit, it enters A/D sampling. In order to ensure that spectrum aliasing does not occur, the sampling rate of the ADC is designed to be 8 times the signal bandwidth, that is, 20.48MHz. Regarding the selection of the second intermediate frequency and the determination of the sampling rate, please refer to the reference 3 and will not be repeated here. The data rate of the sampling reaches 14bit × 20.48 mhhh = 286.72 mbit / s. After the FIFO is buffered, it is sent to DSP for orthogonal transformation, FFT, frequency point recognition and jumping, channel decoding. The following focuses on the detailed description of the hardware implementation of the intermediate frequency digital processing module. 2 Hardware circuit design of intermediate frequency digital processing module As can be seen from Figure 1, the main function of the IF digital processing module is to perform A/D conversion on the 5.12MHz IF bandpass signal and buffer the sampled data into the DSP for processing. The hardware design mainly includes the use of three devices, ADC, FIFO, and DSP, and the two interfaces between them, which are introduced separately below. 2.1 ADC devices The ADC sampling rate requirement is 20.48MHz. For 2-30MHz HF signals, at this sampling rate, the dynamic range of the ADC device is required to reach 60-90dB. The AD6644 of the American AD Company is an ideal choice. AD6644 is an A/D converter with 14-bit precision and a maximum sampling rate of 65MSPS. The main features are: multi-tone spurious free dynamic range (SFDR) reaches 100dB, typical SNR is 74dB, power dissipation is 1.3W, digital sampling output is 2's complement format, and has data output indication signal DRY. AD6644 provides a sample and hold circuit and reference potential on-chip, making it a complete A/D conversion solution. The conversion sensitivity of the AD6644 reaches 134μV, and an SFDR of 100dB is obtained at the Nyquist bandwidth, which greatly enhances the ability to detect useful small signals when there are spurious components at its input end. This breakthrough improvement relaxes the Performance bottlenecks of analog-to-digital receivers (software radios). AD6644 internally adopts a three-level sub-area conversion structure, which not only ensures accuracy but also reduces power consumption. Its internal structure block diagram is shown in Figure 2.

2.1.1 Sampling circuit The sampling clock of the AD6644 requires high quality and low phase noise. If the clock signal jitters greatly, the signal-to-noise ratio will easily deteriorate, making it difficult to ensure 14-bit accuracy. In order to optimize performance, the sampling clock signal of the AD6644 adopts a differential form. The clock signal can be AC-coupled to the ENCODE and ENCODE pins through a transformer or capacitor. These two pins are biased on-chip and require no external bias circuitry. In order to improve the differential input quality of the clock signal, this design uses Motorola's low-voltage differential receiving chip MC100LVEL16. The entire AD6644 sampling circuit is shown in Figure 3. Since the performance of the sampling circuit is related to the final sampling accuracy, when wiring, the distance from the crystal oscillator to the clock input pin should be as short as possible, and the sampling circuit should be isolated as much as possible from other digital circuits. A large area of auxiliary copper should be grounded under the entire sampling circuit to reduce possible electromagnetic interference and also reduce interference to other circuits.

2.1.2 Analog signal input As a new high-speed, large dynamic range ADC, the analog signal input of the AD6644 also requires a differential form. In this way, in the analog signal stage, the differential signal can filter out even-order harmonic components and common-mode interference signals (such as noise introduced by the power supply and ground), and also has a good filtering effect on the feedback signal of the crystal oscillator, which is beneficial to improving the performance of the AD6644 . The analog input voltage of the AD6644 is biased to 2.4V inside the chip, and the analog signal driving the AD6644 is sent to the input terminal through AC coupling. The differential input impedance of the AD6644 is 1kΩ, and the peak-to-peak value of the differential input voltage is 1.1V, so the analog input power is -2dBm, which greatly simplifies the analog signal drive amplifier circuit. Taking full advantage of the high input impedance of AD6644, according to the transformer impedance transformation and optimal impedance matching theory, the reference circuit shown in Figure 4 can be used in practical applications. Then the signal input end can be connected with a matching impedance of 50Ω and a full-scale driving power. An analog signal source of approximately 4.8dBm. The series resistor on the secondary side of the transformer acts as an isolation and current limiting function.

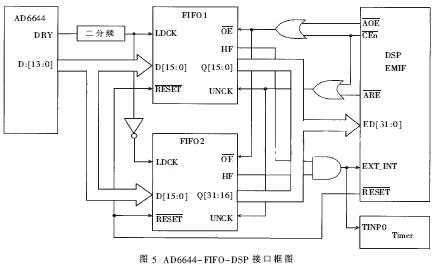

2.1.3 Application Notes The power supply of the AD6644 must have good stability. Since the high-frequency component of the power supply is prone to radiation, a 0.1μF decoupling capacitor should be placed close to each power supply pin of the AD6644. In order to prevent high-speed digital output changes from coupling switching current into the analog power supply, the digital power supply and analog power supply of the AD6644 should be separated. The analog power supply should be within the range of 5V±5%, and the digital power supply should be 3.3V. At the same time, place a 0.1-0.01μF ceramic capacitor as close to the power supply as possible for high-frequency filtering, and place a 10μF tantalum capacitor filter in parallel. Remove low frequency noise. In order to well receive the digital output signal of the AD6644, the capacitive load should be minimized. The digital output of AD6644 has a fixed output conversion swing rate (1V / NS), a typical CMOS door plus a capacitor of about 10PF, so the conversion of each BIT will have 10mA (10PF × 1V / 1NS) dynamic current. Entering and exiting the device, a full-scale conversion dynamic current may reach a maximum of 140mA (14bit×10mA/bit). In practical applications, a 100Ω resistor should be placed on each data output line in order to limit the flow of these currents into the receiving device. It should also be noted that additional capacitive loads will increase transmission delays. To meet the delay requirements of digital output, capacitive loads should be limited to 10pF. 2.2 FIFO device The AD6644 output data rate is as high as 286.72Mbit/s. Such a high data rate will overload the DSP if it is received directly using the EMIF interface of the DSP. In addition, if the storage control system cannot receive data in time, the last data will be immediately updated by the next data, causing data loss, so cache must be used. Currently, the commonly used caches are FIFO, SRAM, dual-port RAM, etc. Dual-port RAM and SRAM have larger storage capacity, but must be equipped with complex address generators. For the FIFO chip, data enters and exits sequentially, and allows data to be written and read at different rates, and the peripheral circuit is simple, so this design uses TI's trigger FIFO SN74ACT7804 as the data cache. SN74ACT7804 is a high-speed 512×18bit FIFO device with an access speed of up to 50MHz and a data access time of up to 15ns. Data is written on the rising edge of LDCK and read on the rising edge of UNCK. The status of the FIFO can be obtained through the status bits: full (/FULL), empty (/EMPTY), half full (HF) and nearly empty/nearly full (AF/AE). SN74ACT7804 can only be powered on and reset. 2.3 DSP devices Due to the high data rate output of the ADC, there will be great pressure to use DSP for real-time processing. Before the DSP can perform operations, digital downconversion must be performed to reduce the data rate. Through the overall analysis of the calculation volume of the DSP algorithm, TI's TMS320C6201 can meet the design needs. As a fixed-point DSP, TMS320C6201 has a main frequency of up to 200MHz and a processing speed of up to 1600MIPS. Its external memory interface (EMIF) supports various synchronous and asynchronous memories and has good support for FIFO. 2.4 Hardware interface design In order to ensure that the sampling output signal of the AD6644 is sent to the DSP accurately and efficiently, two FIFOs are paralleled between the ADC and the DSP to form a dual FIFO buffer structure, and are connected to the DS with a 32bit bus width. P's EMIF interface, the specific connection is shown in Figure 5 shown. Through this interface design, while making full use of the 32-bit data line width of EMIF, it also cleverly realizes the parity and even separation of sampling data, which provides convenience for DSP's digital filtering and FFT operations.

First, the interface between ADC and FIFO is introduced. The 14-bit sampling signal output D130 of the AD6644 is connected to the data input D150 of the two FIFOs (D15 and D14 of the FIFO are suspended), and the DRY signal is After dividing by two, connect the lower 16-bit FIFO1 all the way The LDCK pin of FIFO2 is connected to the LDCK pin of FIFO2 after being inverted by the "NOT" gate. The DRY pin outputs the same-frequency reverse delayed signal of the ENCODE signal. It can be seen from the timing diagram in Figure 6 that at the rising edge of DRY, the sampling signal D130 is ready to be output, and the DRY signal can accurately be used as the trigger storage clock signal for the subsequent FIFO. The DRY signal divided by two alternately triggers the write clocks of FIFO1 and FIFO2 at the rising edge, and stores the odd and even sampling signals into different FIFOs respectively.

Next, the interface between FIFO and EMIF is introduced. For the operation of reading FIFO, the EMIF asynchronous memory control signal is used here: output enable AOE and read enable ARE, CEn are external space selection signals. It can be seen from the logical relationship in the figure that when AOE and CEn are both valid, OE is valid and the chip select enables two FIFOs. When CEn and ARE are valid at the same time, UNCK is invalid, and the data to be read out is initialized at this time. Then ARE will jump to a positive level 4, causing UNCK to generate a rising edge, and the data in FIFO will be read out. In the figure, the half-full signals HF of the two FIFOs are connected to the DSP external interrupt pin EXT_INT through an "AND" gate, and the status of the HF pin is continuously detected during operation. When both FIFOs reach half full, the AND gate output changes from low to high, and the rising edge triggers the DSP external interrupt EXT_INT. DSP starts DMA (direct memory access) to read FIFO data in bursts. The data in FIFO1 is used as the lower 16 bits, and the data in FIFO2 is used as the upper 16 bits, which are combined into 32-bit data and read into the DSP internal storage space. 3 Wiring debugging experience and conclusion Since this module involves high-speed analog-digital mixed circuit design, the circuit board should be strictly divided into analog areas and digital areas, with ADC as the boundary between the two areas. The inner ground should also be divided into digital ground and analog ground accordingly, and connected at one point through magnetic beads near the ADC to eliminate interference from the digital ground to the analog ground. The ADC clock and analog signal input should be isolated as much as possible, and the crystal oscillator should be placed as far away from the power supply circuit as possible. For FIFO, in order to ensure that LDCK, UNCK, HF, RESET and other signals are correct and have good waveforms, and to ensure that data reading will not cause loss or misreading, the interference to these signal lines should be reduced, and the wiring can be appropriately thickened and thickened. Signal package ground measures. During the actual debugging process, it was found that due to the small driving capability of the AD6644's DRY signal output, the FIFO data sometimes missed reading. Using gate circuits for shaping and driving, the phenomenon of missed readings can be solved. This design uses a small number of integrated chips supplemented by a few discrete components to realize the function of the intermediate frequency digital processing module, and the accuracy and reliability are guaranteed to a certain extent. The FIFO buffer interface that separates parity and even data between ADC and DSP can not only reduce the data rate, but also provide parity separation for subsequent algorithms such as polyphase filtering. After debugging, when the receiving system inputs an analog signal with an intermediate frequency of 5.12MHz and a bandwidth of 2.56MHz, its sampling accuracy can be guaranteed to be more than 12 bits, which meets the requirements of DSP signal processing. | ||||||

Previous article:Design of numerically controlled delay device based on field programmable gate array

Next article:Using FPGA to implement multi-channel voice/data multiplexing equipment

Recommended ReadingLatest update time:2024-11-16 21:58

- Popular Resources

- Popular amplifiers

- Huawei's Strategic Department Director Gai Gang: The cumulative installed base of open source Euler operating system exceeds 10 million sets

- Analysis of the application of several common contact parts in high-voltage connectors of new energy vehicles

- Wiring harness durability test and contact voltage drop test method

- Sn-doped CuO nanostructure-based ethanol gas sensor for real-time drunk driving detection in vehicles

- Design considerations for automotive battery wiring harness

- Do you know all the various motors commonly used in automotive electronics?

- What are the functions of the Internet of Vehicles? What are the uses and benefits of the Internet of Vehicles?

- Power Inverter - A critical safety system for electric vehicles

- Analysis of the information security mechanism of AUTOSAR, the automotive embedded software framework

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

Professor at Beihang University, dedicated to promoting microcontrollers and embedded systems for over 20 years.

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- New real-time microcontroller system from Texas Instruments enables smarter processing in automotive and industrial applications

- 【AT-START-F425 Review】 VII. SPI Driver RC522 Card Reader Review

- [Mil MYC-J1028X development board trial] High-speed network data transmission test

- 【Multi-function network weather clock】Material unboxing - ESP32-S2-Kaluga-1

- Please recommend a low voltage drop Buck chip

- [DFRobot motor driver] + DC motor driver Arduino example program analysis

- Four major causes of board bending and warping

- Today's Live Broadcast: ADI Motor Control Solutions

- How is BQ40Z50 charging management achieved?

- The show starts at 10am today: Interpretation of TI's latest low-cost C2000 features, quickly getting started with precision power supply and motor control!

- Buck high-side driver (PMOS)

ESP32-S3 source code

ESP32-S3 source code 【Follow me Season 2 Episode 2】Arduion UR4 homework submission code

【Follow me Season 2 Episode 2】Arduion UR4 homework submission code MCU C language programming and Proteus simulation technology (Xu Aijun)

MCU C language programming and Proteus simulation technology (Xu Aijun)

京公网安备 11010802033920号

京公网安备 11010802033920号