Signal integrity ( SI ) issues are becoming a growing concern for digital hardware designers. As data rate bandwidths increase in wireless base stations, wireless network controllers, wired network infrastructure, and military avionics systems, circuit board designs are becoming increasingly complex.

High-speed serial links between chips are now widely used to improve overall throughput performance. Processors, FPGAs , and digital signal processors can transfer large amounts of data to each other. In addition, this data may have to be sent from the circuit board, through the backplane to the switch card, which can send the data to other cards in the chassis or elsewhere in the "system". RapidIO -enabled switches enable interconnection between these different components and are widely used to meet the real-time bandwidth needs of these applications.

This article focuses on the signal integrity challenges involved in high-speed interface designs (the main functions of the RapidIO switch support these high-speed interface designs) and other related issues. The functions of the RapidIO switch are optimized to achieve high signal integrity in high-speed designs.

High-speed interface design challenges

Signal quality is important in every aspect of a system. For Serial RapidIO, signal quality is quantified by the size of the receive eye diagram. The receive eye diagram is an infinitely continuous trace where the waveform repeats itself over and over again as the previous trace (see Figure 1). The larger the eye opening, the better the signal quality.

Signal quality can be affected by many factors: the presence of noise or other clutter in the signal path, poor signal path routing, conduction or radiation from external sources, and noise generated by the system itself. All of these factors combined can result in a narrow receive eye diagram. In addition to board-level issues, signal integrity can also be affected by the source (transmitter) and destination (receiver) of the connection. Therefore, the characteristics of the source and destination ICs should be considered in the overall system-level signal integrity.

Board-Level Design Considerations

When it comes to board design, common factors to consider include:

1. Power input of the circuit board, output of the local regulator and distribution

2. Clock generation and distribution

3. Decoupling

4. PCB basic materials

5. Inter-chip connection

6. Connection between circuit boards and backplane

7. Circuit board stacking and impedance control

8. Inter-rack connectors, cables and joints

Figure 1: Typical high-speed signal eye diagram.

When operating above 300MHz, most of the design best practices that apply to lower frequency board design need to be modified. Factors that arise when wavelengths are comparable to board size must be considered. This applies not only to the wavelength of the fundamental frequency, but also to the Fourier (frequency domain) components that make up the complete waveform.

FR4 material can still be successfully used as the base material for the circuit board, but at higher frequencies, not only the dielectric constant of the material needs to be considered, but also the loss factor. The design of the vias also becomes very important because the impedance of the unused tube length (whose effect can be ignored at lower frequencies) will not match the impedance of the thicker circuit board and backplane. It is best to complete post-design simulation to draw attention to routing that is less than ideal for signal integrity and point out areas of crosstalk.

Specific challenges with signal integrity on circuit boards arise from the presence of high-speed processor buses and high-speed memory interfaces, clock generation and clock noise, and various board noise sources, typically including: single-ended parallel buses, power distribution, impedance matching, ground bounce, crosstalk, and clock generation.

Serial RapidIO Switches

Serial RapidIO interconnects can be used to address some of the signal integrity challenges discussed above. RapidIO is a mature, open standard for chip-to-chip, board-to-board, and chassis-to-chassis interconnects designed by leaders in embedded computing to meet the reliability, cost-effectiveness, performance, and scalability requirements of equipment in the wireless infrastructure, networking, storage, scientific, military, and industrial markets.

RapidIO is a point-to-point packet switching interconnect protocol designed to meet the needs of current and future embedded applications. The RapidIO Physical Layer 1x/4x Link Serial Specification meets the physical layer media requirements of devices using electronic serial connections. The specification defines a full-duplex serial physical layer interface (link) between devices using unidirectional differential signaling. In addition, it allows four serial links to be grouped together for applications that require higher link performance. It also defines protocols for link management and the transmission of packets over the link.

The architecture of the RapidIO system consists of endpoint components and the switching fabric that connects the endpoints. Imagine the endpoint as the starting point in the mail system and the switch as the post office that intercepts the package and sends it to the destination. The RapidIO interconnect architecture is divided into a layered architecture according to the specification, including the logical layer, the common transport layer, and the physical layer. The physical layer of the RapidIO protocol is handled by the chip serializer-deserializer (SerDes). The characteristics of the SerDes have a certain impact on the signal integrity issues that hardware designers face when designing circuit boards. Many other aspects of the switch design will also affect signal integrity.

RapidIO switch features simplify board design and provide high signal integrity

Clock Generation

As an enabler, the sRIO switch must have a noise-free clock signal to achieve low jitter. Low jitter signals are basically characterized by low phase noise. If the input clock signal is increased to achieve higher frequency output signals, the chip circuit must be optimized to produce minimal phase noise. Tundra's Tsi57x Serial RapdIO Switches generate output signals up to 3.125Ghz by using 125MHz and 155MHz clocks with integrated low noise amplifier PLLs. Many products use independent circuits to achieve these functions, so they cannot achieve the low jitter like Tundra switches. The clarity of the output signal is also not as good as when using Tundra switches, making it difficult for board designs to tolerate the other board-level signal integrity issues discussed above.

Programmable transmit pre-emphasis and receiver equalization

In high-speed board design, you need to consider the attenuation of the signal as it travels through the board from chip to chip or across a backplane. Simply put, the actual signal is reduced in strength and may be phase shifted by the time it reaches the endpoint. In general, in all media, high-frequency harmonics are attenuated more proportionally than lower-frequency harmonics. Simply boosting the overall signal is not enough because it expands the noise floor and does not address the phase shift issue. Serial RapidIO switches and endpoints (like all other high-speed designs such as GbE and 10GbE) use technology to avoid this problem and maintain the integrity of the original signal.

To understand the impact of transmit pre-emphasis and receiver equalization, recall that the goal of an eye diagram is to achieve an “open eye.” Without these techniques, the eye diagram will begin to “close.”

Transmit pre-emphasis technology can add high frequencies to the transmission signal to solve the problems of signal attenuation and phase shift between endpoints. Therefore, unlike simply amplifying all frequencies (this method also increases the overall power consumption of the switching chip), transmit pre-emphasis can effectively enhance the output waveform through the transmission function, increase the high frequency content of the output waveform, and at the same time use virtual components to phase shift it to solve the phase shift caused by the transmission medium. This method is very effective in maintaining signal integrity and maintaining eye diagrams. Figure 2 illustrates the impact of using transmit pre-emphasis.

Figure 2: Effect of transmit pre-emphasis on eye diagram.

Although transmit pre-emphasis is commonly used in many high-speed ICs to optimize overall system-level signal integrity, transmit pre-emphasis on the "transmit side" should be used in conjunction with receiver equalization on the "receive side." Receiver equalization applies the function of a transmit enhancer to compensate for high-frequency transmission losses and phase shifts caused by circuit boards and backplanes. Since these transmission losses occur before the signal reaches the destination IC (in this case, the Serial RapidIO switch), the switch must typically take steps to compensate for these losses before the signal is sent to the next transmission section (another switch) or endpoint in the system. Receiver equalization works similarly to transmit pre-emphasis and improves the overall signal-to-noise ratio. Note: Each link connected to the switch chip may have different characteristics.

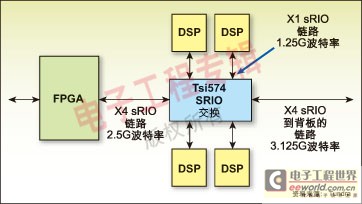

Figure 3: Wireless baseband switch with Serial RapidIO switching and various link rates.

For example, in Figure 3, the link to the FPGA may traverse multiple areas on the board and may pass through several layers and be affected by EMI , while the link to the DSP from the switch may run at a lower speed and a relatively short distance. Finally, the backplane link may also have a higher speed and pass through multiple connectors. The attenuation characteristics of the above three links in terms of amplitude and phase are different as shown in Figure 4.

Figure 4: The received signal is affected by different links.

Synchronous and asynchronous switching design

The Serial RapidIO standard supports three different link rates: 1.25G baud, 2.5G baud, and 3.125G baud. Switching can be divided into two categories: synchronous and asynchronous.

Synchronous switching refers to switching in which all ports must operate at the same speed.

Asynchronous switching refers to switching in which each port can operate at the frequency required by the traffic demands of a particular link.

In most applications, the best solution is asynchronous switching, which not only has the advantage of being able to meet the communication volume requirements at a lower overall system power consumption, but also is less affected by crosstalk in terms of signal integrity.

Packaging and interconnection

Signal integrity issues can be greatly affected by the design of the packaging and base materials. For example, high-performance flip-chip and wire-bond packaging can improve power delivery and reduce return loss. For RapidIO switches, it is important to improve impedance matching to maintain 100 ohm differential impedance and low variation. Flip-chip packaging can help improve this.

Efficient spherical mapping

Silicon vendors may choose ball mapping to simplify signal routing from the chip to the ball grid, but it does more than that. Ideally, the ball mapping is designed with the overall system-level implementation in mind. For example, the ball mapping must be designed with the peripheral ICs connected to the switch chip in mind. The design should be optimized to minimize the number of layers and the required area, which will improve the signal integrity of the final design. ICs with relatively dense ball mappings require many layers on the board to route signals out of the IC, resulting in a costly system-level design. Another issue is crosstalk between signal channels, which was mentioned earlier when discussing the difference between synchronous and asynchronous RapidIO switches. Closely related to crosstalk between signal channels and efficient ball mapping is the spacing between power and ground pins. If too many Serial RapidIO ports are packed into a small package, signal integrity issues can occur due to crosstalk, resulting in "eye closure" of signals as they travel from the switch to the endpoints.

Design Conventions Tips

Now, let's review another aspect of signal integrity, which is the design issues at the board level. Designers can take many design guidelines to control the effects of noise. In general, good design practices can help board designers control the signal noise generated by board-level communication, including limiting external noise sources and addressing noise in the device itself.

First, all designs should use the correct trace width, spacing, and topology to ensure that the impedance of each trace matches its transmission device. Impedance mismatch may affect the quality of the leading and trailing edges, settling delay time, crosstalk, and EMI.

Adequate channel spacing between synchronous signal groups must be ensured, channel length must be limited, and skew between differential pair signals must be minimized. Routing should minimize the number of routing layer transitions to limit parasitic effects. Vias in unnecessary inductance and stray capacitance are very costly and should be minimized. In addition to the BGA pad, a maximum of two vias are generally allowed per channel.

Thorough verification of signal integrity is critical. Pre-design analysis using estimated parasitics provides the data needed to understand the performance of a design, but accurate post-design parasitics provide the detail needed to uncover potential signal integrity issues. Using this approach, a circuit netlist is created to simulate and document the results.

Good signal integrity can be achieved if channels and signal paths are kept as short as possible, shielded by ground planes or physically isolated from each other, and care is taken to avoid impedance mismatches or any configuration that would cause resonance.

Select Serial RapidIO switch chips to achieve high signal integrity

How do designers select a Serial RapidIO switch? Just as good design practices can help board designers control the signal noise generated by board-level communications, hardware designers need to actively consider the characteristics of clock generation, transmit pre-emphasis and receiver equalization, optimized packaging technology, effective spherical mapping, and asynchronous design of Serial RapidIO switches to ensure high signal integrity at the system level. Obviously, when choosing a serial interface, the chip selected by the designer must not only have the right features, but also must be a switch chip designed specifically to solve high-speed signal problems.

Currently, Tundra Semiconductor Corporation offers three generations of Serial RapidIO switching products with the above features. The Tsi 57x product line includes Tsi574, Tsi576 and Tsi578, each with different port numbers ranging from 4 to 16 ports, and operating speeds ranging from 1.25G to 3.125G. Each port supports optional x1 and x4 channels, and the power consumption of each port is 120 to 200mW. The Tsi57x product line has all the signal integrity features described in this article, including transmit pre-emphasis and receiver equalization. This product has added some new features compared to the previous Tsi56x product line, including multicast capabilities and matrix performance monitoring. In addition, many advanced communication management functions have been optimized to meet the high performance requirements of applications such as wireless base stations, wireless network controllers, wired network infrastructure, and military avionics systems.

Conclusion

Through the above analysis, it can be found that if you are familiar with the basic design rules, you can avoid any traditional problems related to poor signal integrity when applying high-frequency interconnects (such as Serial RapidIO) in the system, such as noise, transient effects, crosstalk or jitter.

Previous article:System DC power supply selection affects test throughput

Next article:How to perform internal and external calibration of computer-based measuring instruments

Recommended ReadingLatest update time:2024-11-17 03:46

- Keysight Technologies Helps Samsung Electronics Successfully Validate FiRa® 2.0 Safe Distance Measurement Test Case

- From probes to power supplies, Tektronix is leading the way in comprehensive innovation in power electronics testing

- Seizing the Opportunities in the Chinese Application Market: NI's Challenges and Answers

- Tektronix Launches Breakthrough Power Measurement Tools to Accelerate Innovation as Global Electrification Accelerates

- Not all oscilloscopes are created equal: Why ADCs and low noise floor matter

- Enable TekHSI high-speed interface function to accelerate the remote transmission of waveform data

- How to measure the quality of soft start thyristor

- How to use a multimeter to judge whether a soft starter is good or bad

- What are the advantages and disadvantages of non-contact temperature sensors?

- Innolux's intelligent steer-by-wire solution makes cars smarter and safer

- 8051 MCU - Parity Check

- How to efficiently balance the sensitivity of tactile sensing interfaces

- What should I do if the servo motor shakes? What causes the servo motor to shake quickly?

- 【Brushless Motor】Analysis of three-phase BLDC motor and sharing of two popular development boards

- Midea Industrial Technology's subsidiaries Clou Electronics and Hekang New Energy jointly appeared at the Munich Battery Energy Storage Exhibition and Solar Energy Exhibition

- Guoxin Sichen | Application of ferroelectric memory PB85RS2MC in power battery management, with a capacity of 2M

- Analysis of common faults of frequency converter

- In a head-on competition with Qualcomm, what kind of cockpit products has Intel come up with?

- Dalian Rongke's all-vanadium liquid flow battery energy storage equipment industrialization project has entered the sprint stage before production

- Allegro MicroSystems Introduces Advanced Magnetic and Inductive Position Sensing Solutions at Electronica 2024

- Car key in the left hand, liveness detection radar in the right hand, UWB is imperative for cars!

- After a decade of rapid development, domestic CIS has entered the market

- Aegis Dagger Battery + Thor EM-i Super Hybrid, Geely New Energy has thrown out two "king bombs"

- A brief discussion on functional safety - fault, error, and failure

- In the smart car 2.0 cycle, these core industry chains are facing major opportunities!

- Rambus Launches Industry's First HBM 4 Controller IP: What Are the Technical Details Behind It?

- The United States and Japan are developing new batteries. CATL faces challenges? How should China's new energy battery industry respond?

- Murata launches high-precision 6-axis inertial sensor for automobiles

- Ford patents pre-charge alarm to help save costs and respond to emergencies

- First day of the journey in Shenzhen

- Infrared thermal imager recommendation

- V853 Replace the startup LOGO

- The problem of the servo not rotating when the nodemcu esp8266 development board drives it

- Mentor Usage Problems

- Ethernet Problems

- If you want to know whether the signal generated by the signal generator or function generator is ready or whether it is input according to the set value standard...

- MicroPython precompiled firmware for TB-01 (W600)

- Is it necessary to attend Altium's offline training?

- How to prevent audio equipment from aging and make the sound better

RapidIO™ Interconnect Specification

RapidIO™ Interconnect Specification

京公网安备 11010802033920号

京公网安备 11010802033920号