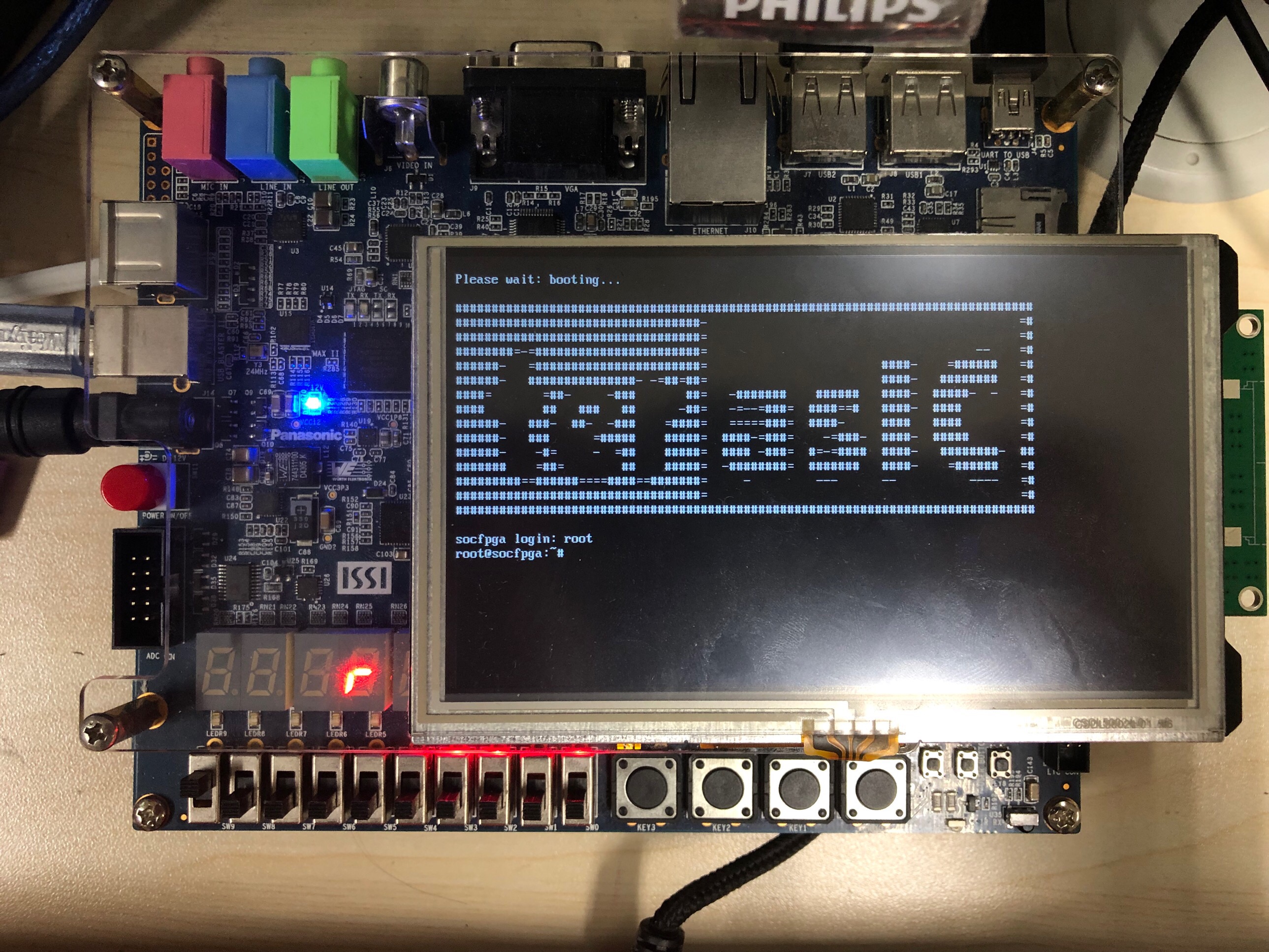

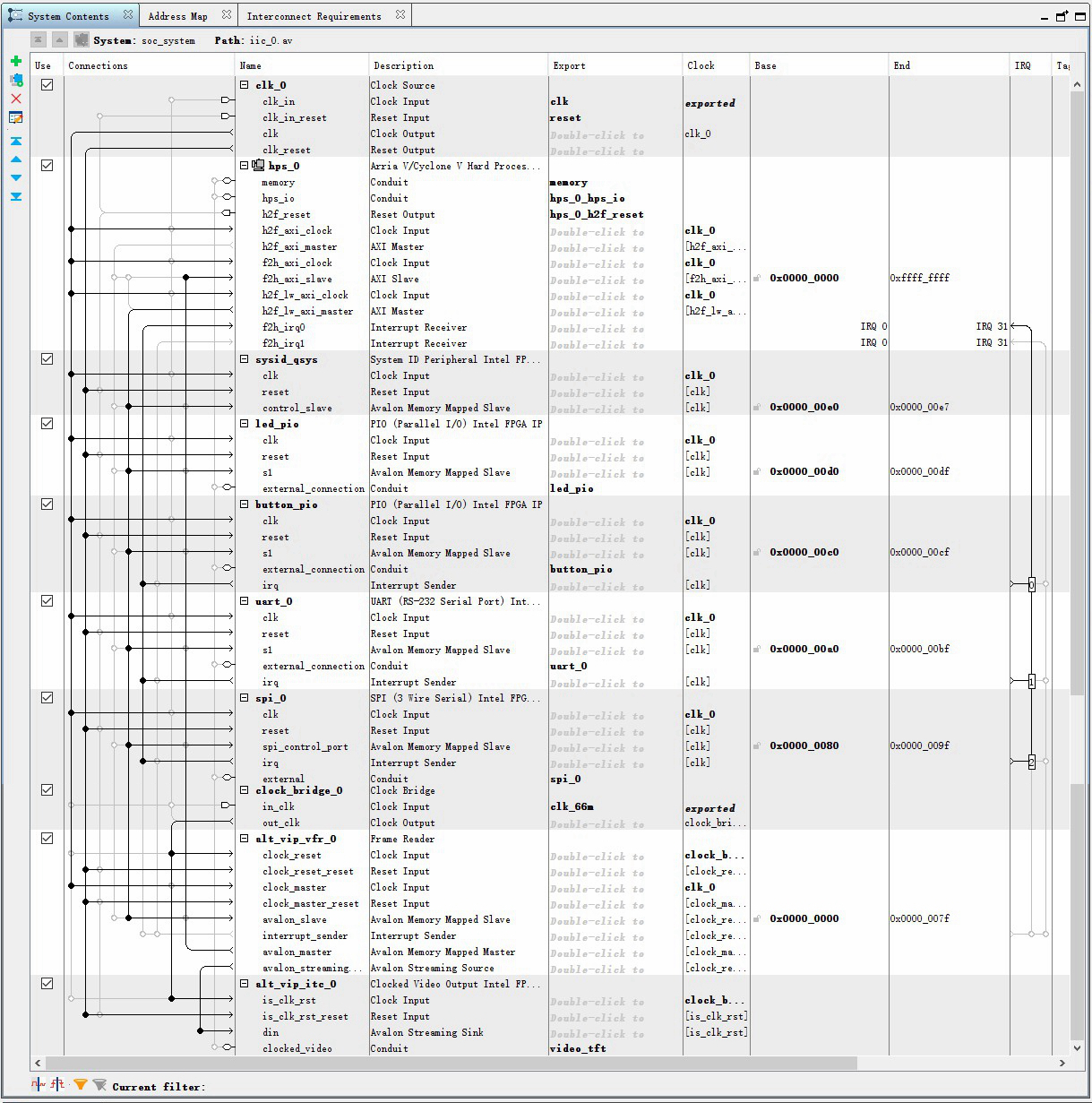

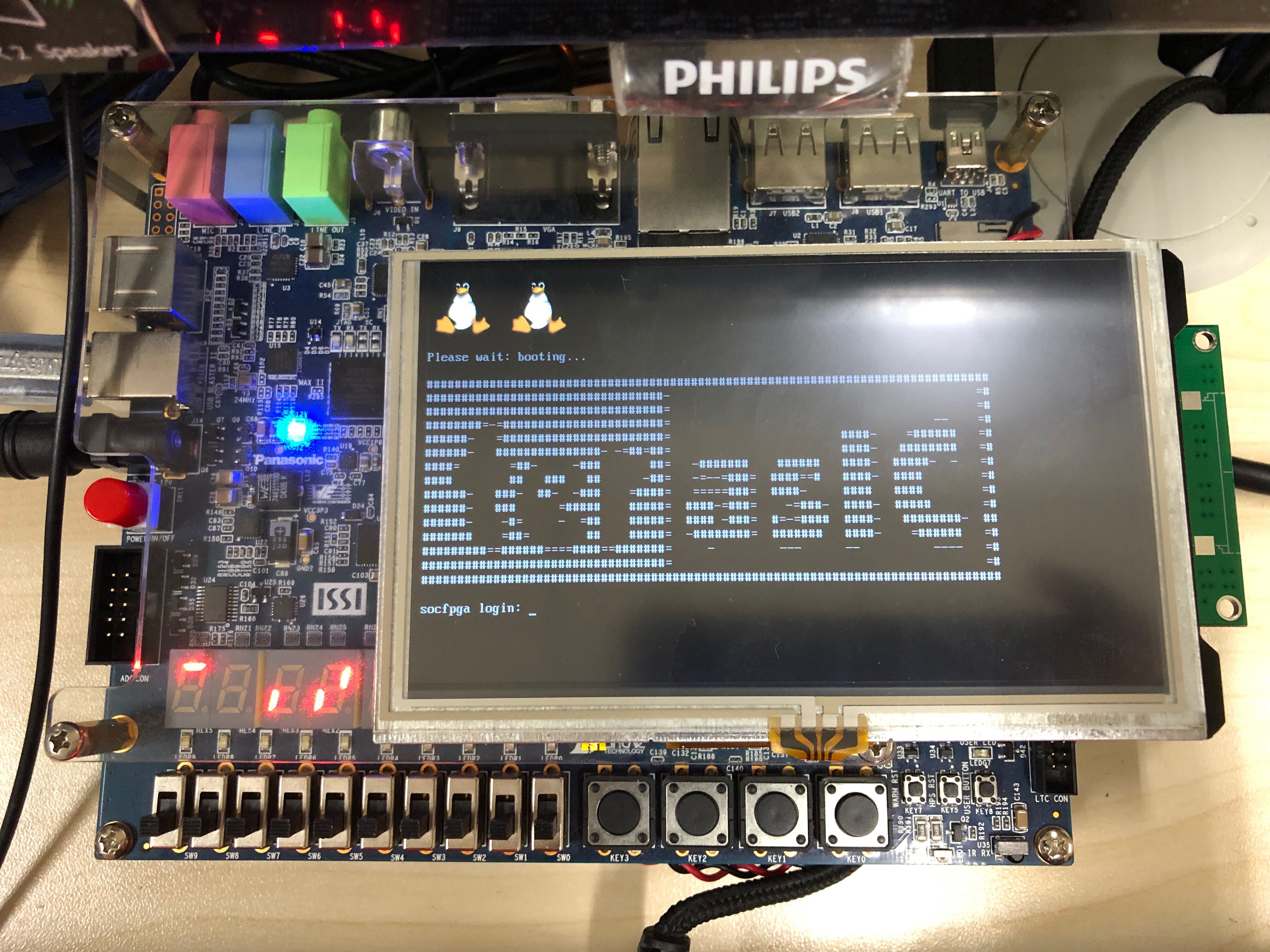

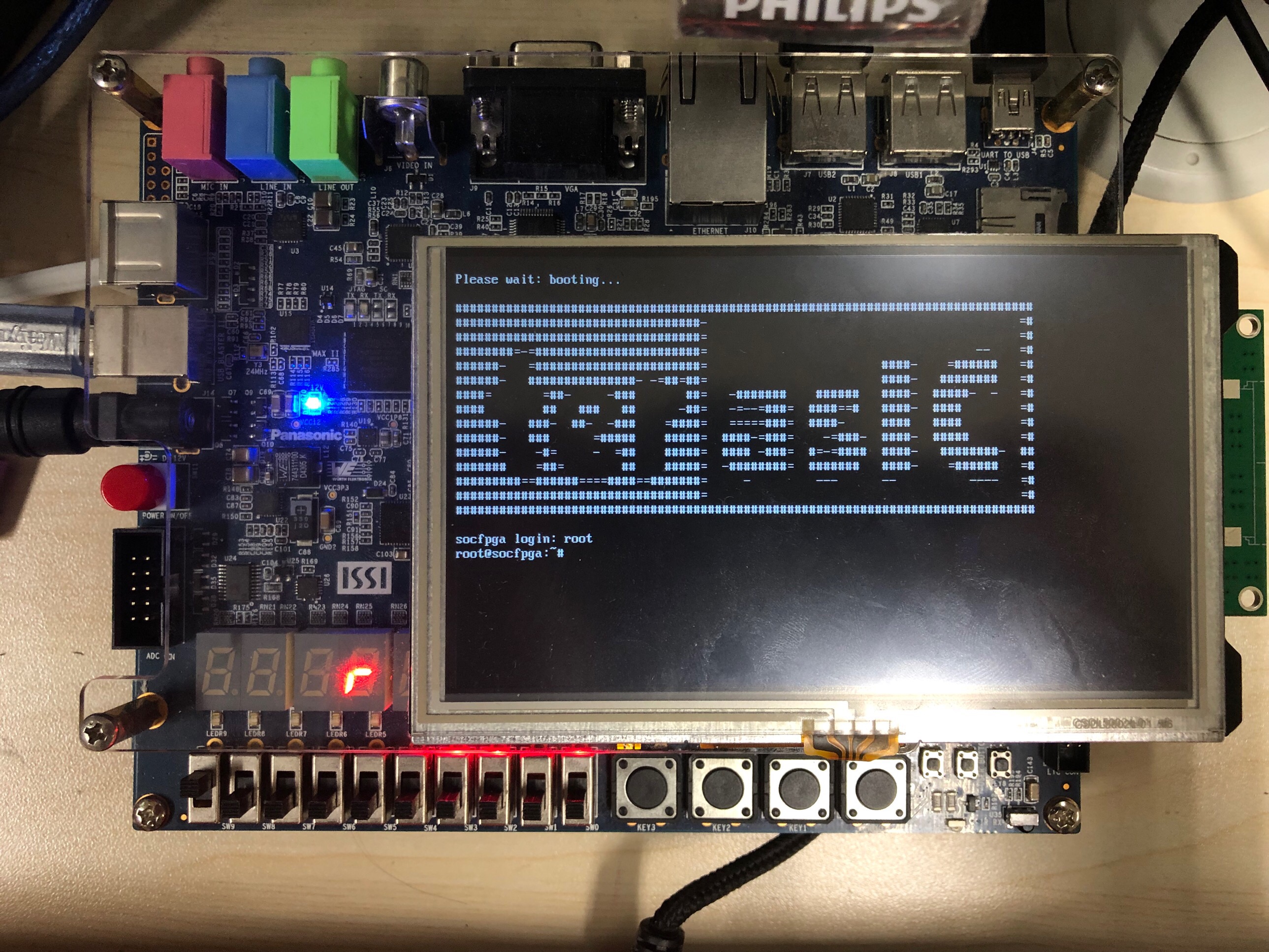

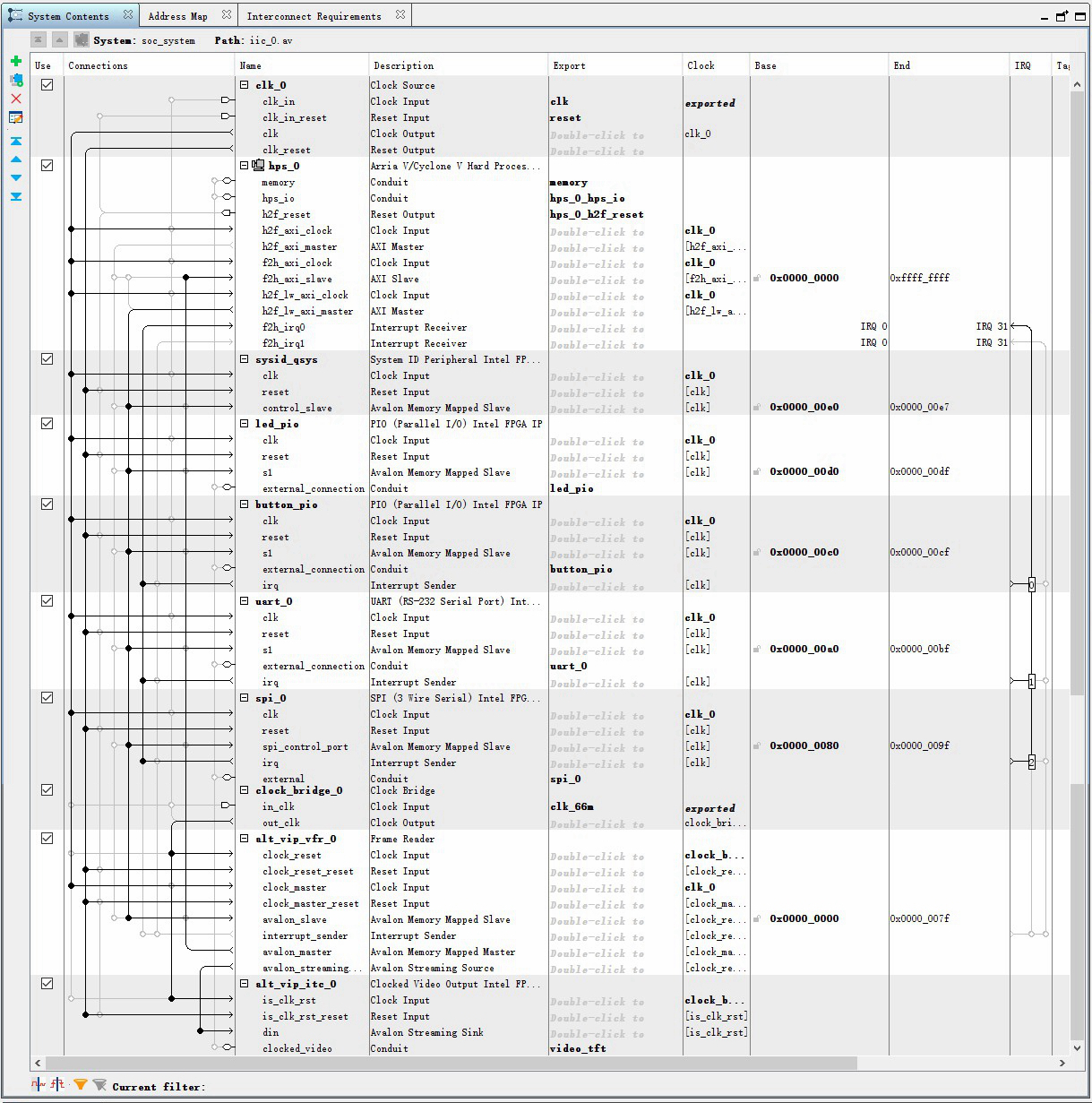

Markdown support is not good, just read the original text: http://verdvana.top/soc/fpga/ver ... 94%AE%E7%9B%98.html]http://verdvana.top/soc/fpga/ver ... 94%AE%E7%9B%98.html ### 1. Introduction I have a DE1-SoC development board (which caused me to eat dirt for 800 months), and according to the Training Manual of Terasic and Xiao Mei Ge and ran some simple routines on it. Later, I saw that Xiao Mei Ge's AC501 development board had a 5-inch TFT touch screen, and the DE1-SoC didn't even have a black and white LCD screen, so I thought about whether I could add Xiao Mei Ge's screen to the DE1-SoC and let the Linux terminal display on the screen, saving the need for an external VGA monitor. If you want to operate completely on DE1-SoC, it is not enough to have a screen, you also need to connect a keyboard to input commands. DE1-SoC has two USB Hosts that can connect USB devices, but you need to add a USB keyboard driver to use them. Take a look at the final effect in the figure above:  You can see that the Linux terminal is displayed on the TFT screen, and then use the USB keyboard to enter the administrator username "root" to enter the system. The following is a detailed description of how to hang these two peripherals on the SoC-FPGA and add drivers for them in the Linux kernel. Development environment: Quartus Prime Standard 18.1 Operating system: Windows 10 Pro 1809 / Ubuntu 18.04 LTS ------- ### 2. Create a new SoC-FPGA project. You can refer to Xiaomei's tutorial, which is linked above. The built "soc_system.qsys" is as shown below:

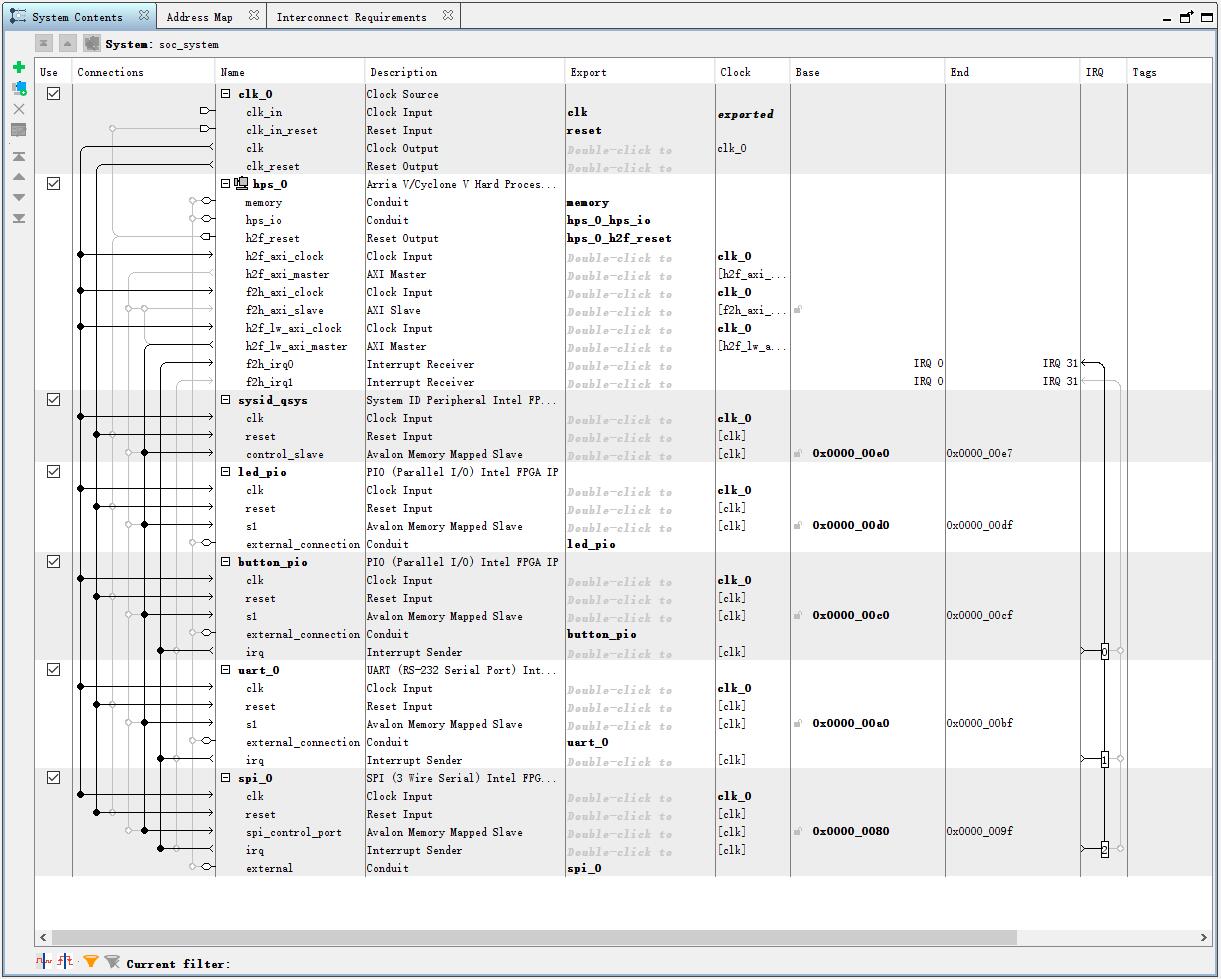

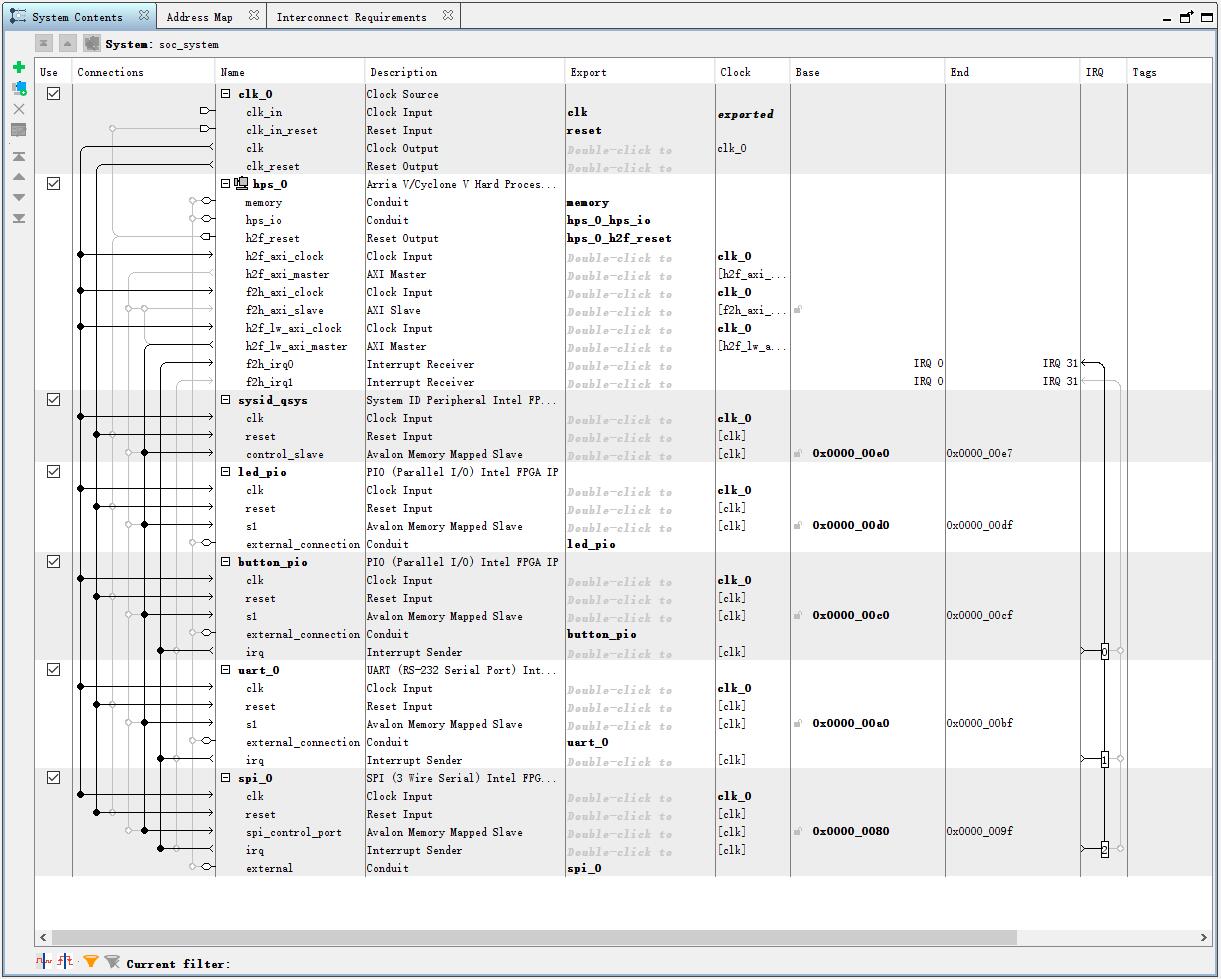

You can see that the Linux terminal is displayed on the TFT screen, and then use the USB keyboard to enter the administrator username "root" to enter the system. The following is a detailed description of how to hang these two peripherals on the SoC-FPGA and add drivers for them in the Linux kernel. Development environment: Quartus Prime Standard 18.1 Operating system: Windows 10 Pro 1809 / Ubuntu 18.04 LTS ------- ### 2. Create a new SoC-FPGA project. You can refer to Xiaomei's tutorial, which is linked above. The built "soc_system.qsys" is as shown below:  --------------- ### 3. Add Frame Reader IP core What is Frame Reader IP core, why to add it, how to add it, in my other article "[Add Frame Reader in Quartus Prime 17.1 and above] IP core](http://verdvana.top/fpga/verilog%20hdl/ip/soc/2019/01/02/%E6%B7%BB%E5%8A%A0Frame-Reader-IP%E6%A0%B8.html)”, so I won’t talk about it here. ### 4. Modify SoC-FPGA project#### 4.1 Modify Qsys First, modify “soc_system.qsys”. Add the Frame Reader, Clocked Video Output, and Clock Bridge IP cores just added to the Qsys system. The Clock Bridge settings are as shown in the figure:

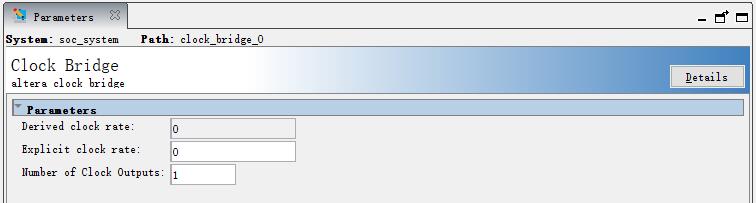

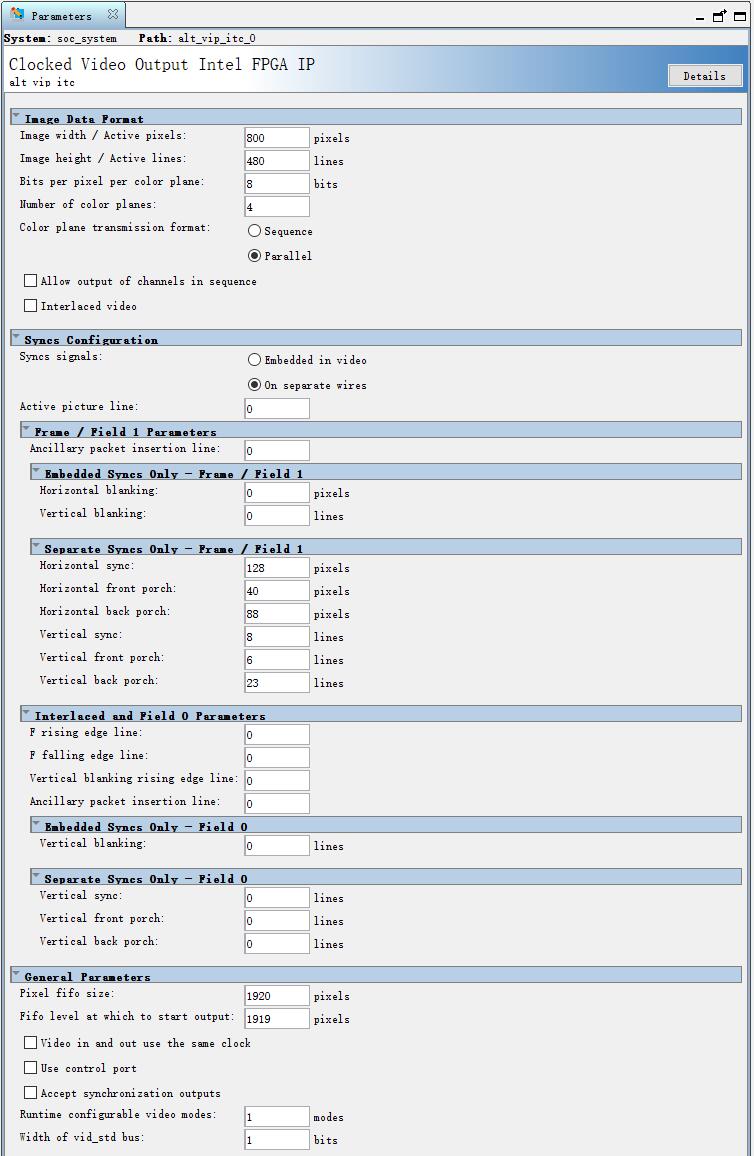

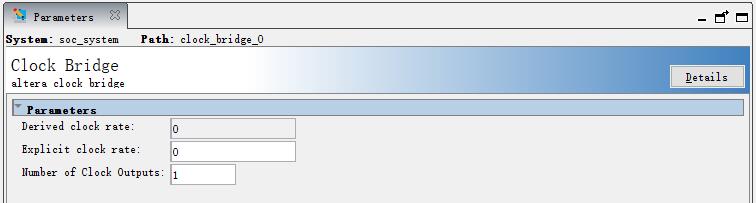

--------------- ### 3. Add Frame Reader IP core What is Frame Reader IP core, why to add it, how to add it, in my other article "[Add Frame Reader in Quartus Prime 17.1 and above] IP core](http://verdvana.top/fpga/verilog%20hdl/ip/soc/2019/01/02/%E6%B7%BB%E5%8A%A0Frame-Reader-IP%E6%A0%B8.html)”, so I won’t talk about it here. ### 4. Modify SoC-FPGA project#### 4.1 Modify Qsys First, modify “soc_system.qsys”. Add the Frame Reader, Clocked Video Output, and Clock Bridge IP cores just added to the Qsys system. The Clock Bridge settings are as shown in the figure:  The Frame Reader settings are as shown:  The Clocked Video Output settings are as shown in the figure:

The Frame Reader settings are as shown:  The Clocked Video Output settings are as shown in the figure:  The wiring method is as shown in the figure:

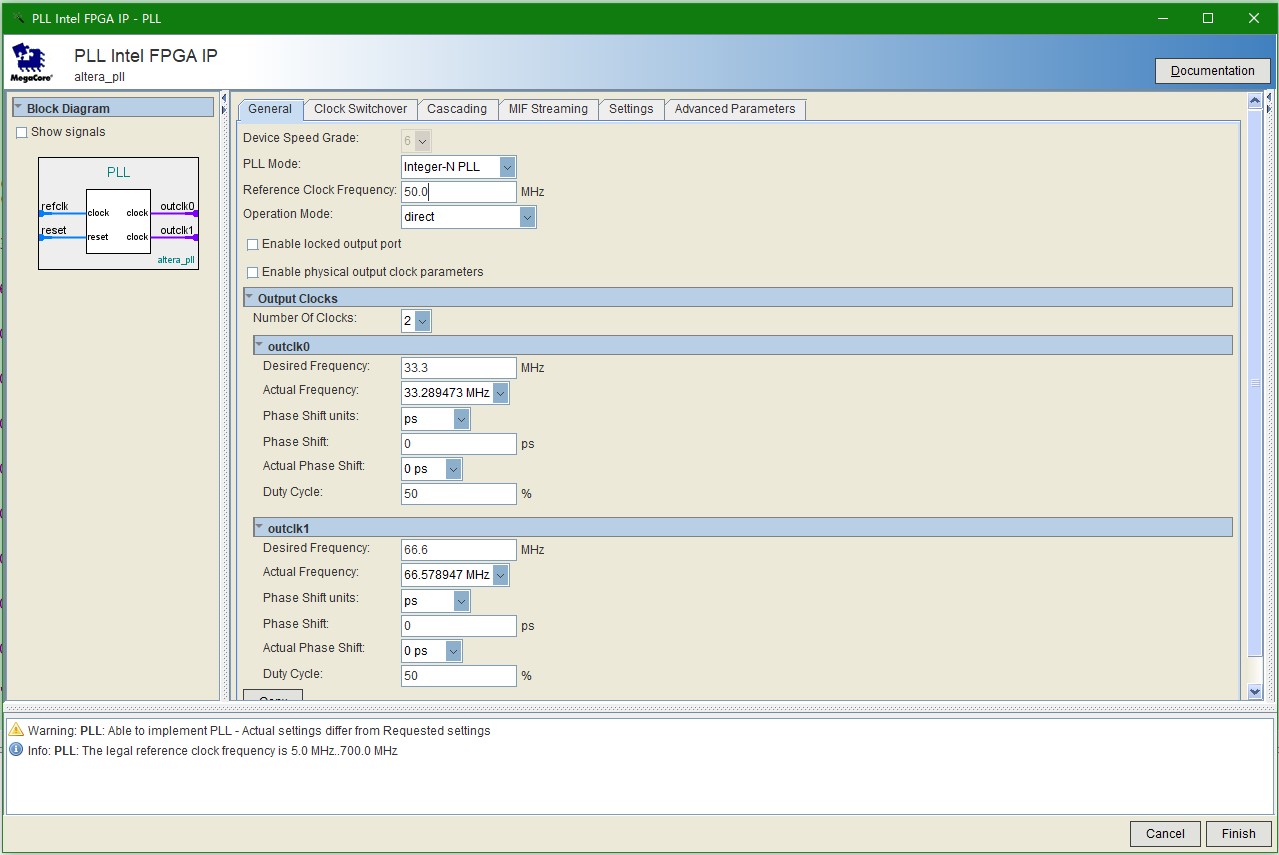

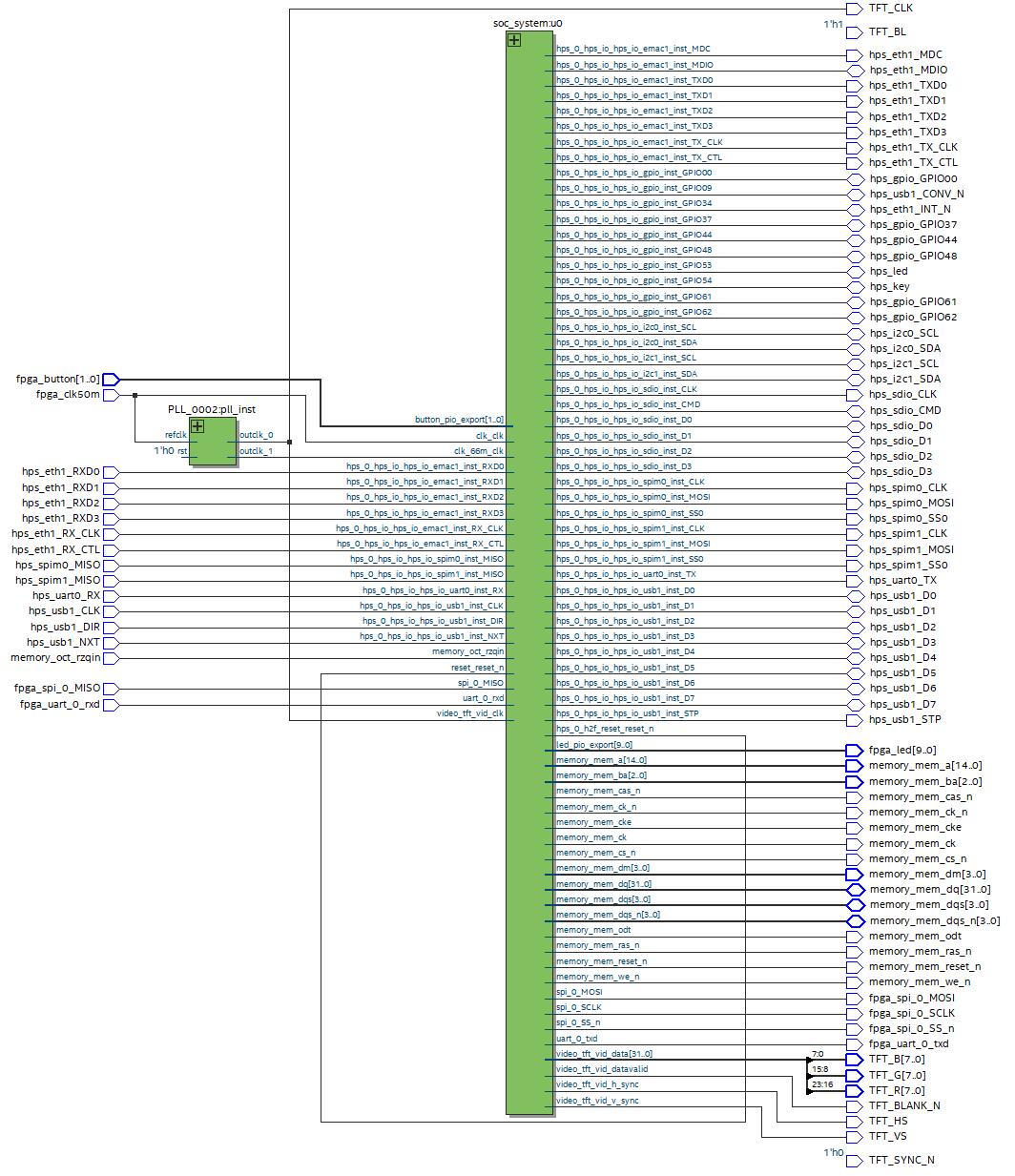

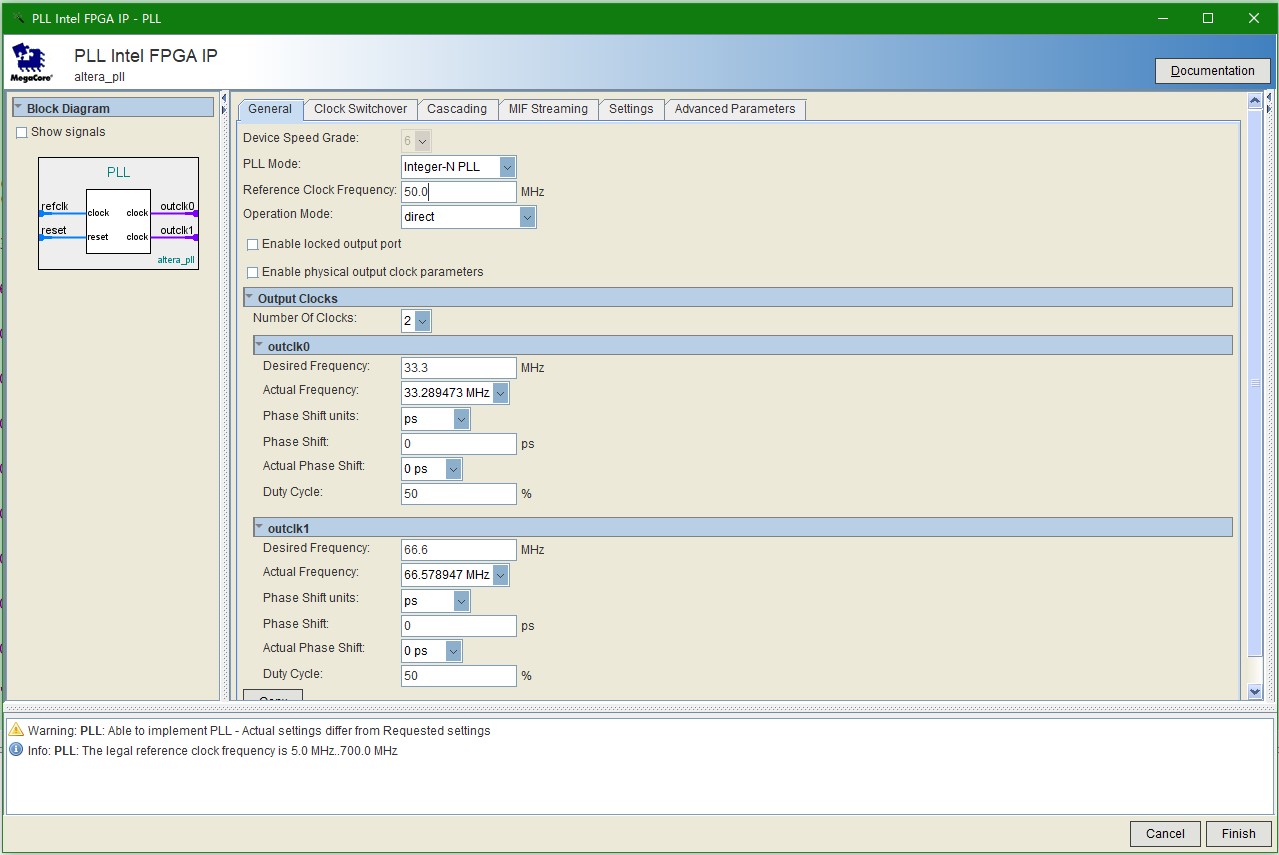

The wiring method is as shown in the figure:  Frame Reader and Clocked Video Output are what we have talked about in the previous article. The Clock Bridge provides clocks for these two IPs. Save and generate HDL. #### 4.2 Modify the top-level file The three IPs just added are needed by the TFT screen, so there are more pins to drive the screen. The Clock Bridge just mentioned also needs a 66.6MHz clock, so a PLL needs to be added. : The parameters of the PLL are as shown in the figure below:

Frame Reader and Clocked Video Output are what we have talked about in the previous article. The Clock Bridge provides clocks for these two IPs. Save and generate HDL. #### 4.2 Modify the top-level file The three IPs just added are needed by the TFT screen, so there are more pins to drive the screen. The Clock Bridge just mentioned also needs a 66.6MHz clock, so a PLL needs to be added. : The parameters of the PLL are as shown in the figure below:  The modified top-level file code is: ``` module DE1_SoC_GHRD( input wire fpga_clk50m, // clk.clk input wire [1:0] fpga_button, // button_pio.export output wire hps_eth1_TX_CLK, // hps_0_hps_io.hps_io_emac1_inst_TX_CLK output wire hps_eth1_TXD0, // .hps_io_emac1_inst_TXD0 output wire hps_eth1_TXD1, // .hps_io_emac1_inst_TXD1 output wire hps_eth1_TXD2, // .hps_io_emac1_inst_TXD2 output wire hps_eth1_TXD3, // .hps_io_emac1_inst_TXD3 input wire hps_eth1_RXD0, // .hps_io_emac1_inst_RXD0 inout wire hps_eth1_MDIO, // .hps_io_emac1_inst_MDIO output wire hps_eth1_MDC, // .hps_io_emac1_inst_MDC input wire hps_eth1_RX_CTL, // .hps_io_emac1_inst_RX_CTL output wire hps_eth1_TX_CTL, // .hps_io_emac1_inst_TX_CTL input wire hps_eth1_RX_CLK, // .hps_io_emac1_inst_RX_CLK input wire hps_eth1_RXD1, // .hps_io_emac1_ins t_RXD1 input wire hps_eth1_RXD2, // .hps_io_emac1_inst_RXD2 input wire hps_eth1_RXD3, // .hps_io_emac1_inst_RXD3 inout wire hps_eth1_INT_N, // .hps_io_emac1_inst_RXD3 inout wire hps_sdio_CMD, // .hps_io_sdio_inst_CMD inout wire hps_sdio_D0, // .hps_io_sdio_inst_D0 inout wire hps_sdio_D1, // .hps_io_sdio_inst_D1 output wire hps_sdio_CLK, // .hps_io_sdio_inst_CLK inout wire hps_sdio_D2,// .hps_io_sdio_inst_D2

inout wire hps_sdio_D3, // .hps_io_sdio_inst_D3

The modified top-level file code is: ``` module DE1_SoC_GHRD( input wire fpga_clk50m, // clk.clk input wire [1:0] fpga_button, // button_pio.export output wire hps_eth1_TX_CLK, // hps_0_hps_io.hps_io_emac1_inst_TX_CLK output wire hps_eth1_TXD0, // .hps_io_emac1_inst_TXD0 output wire hps_eth1_TXD1, // .hps_io_emac1_inst_TXD1 output wire hps_eth1_TXD2, // .hps_io_emac1_inst_TXD2 output wire hps_eth1_TXD3, // .hps_io_emac1_inst_TXD3 input wire hps_eth1_RXD0, // .hps_io_emac1_inst_RXD0 inout wire hps_eth1_MDIO, // .hps_io_emac1_inst_MDIO output wire hps_eth1_MDC, // .hps_io_emac1_inst_MDC input wire hps_eth1_RX_CTL, // .hps_io_emac1_inst_RX_CTL output wire hps_eth1_TX_CTL, // .hps_io_emac1_inst_TX_CTL input wire hps_eth1_RX_CLK, // .hps_io_emac1_inst_RX_CLK input wire hps_eth1_RXD1, // .hps_io_emac1_ins t_RXD1 input wire hps_eth1_RXD2, // .hps_io_emac1_inst_RXD2 input wire hps_eth1_RXD3, // .hps_io_emac1_inst_RXD3 inout wire hps_eth1_INT_N, // .hps_io_emac1_inst_RXD3 inout wire hps_sdio_CMD, // .hps_io_sdio_inst_CMD inout wire hps_sdio_D0, // .hps_io_sdio_inst_D0 inout wire hps_sdio_D1, // .hps_io_sdio_inst_D1 output wire hps_sdio_CLK, // .hps_io_sdio_inst_CLK inout wire hps_sdio_D2,// .hps_io_sdio_inst_D2

inout wire hps_sdio_D3, // .hps_io_sdio_inst_D3

inout wire hps_usb1_CONV_N, // .hps_io_usb1_inst_D0

inout wire hps_usb1_D0, // .hps_io_usb1_inst_D0

inout wire hps_usb1_D1, // .hps_io_usb1_inst_D1

inout wire hps_usb1_D2, // .hps_io_usb1_inst_D2

inout wire hps_usb1_D3, // .hps_io_usb1_inst_D3

inout wire hps_usb1_D4, // .hps_io_usb1_inst_D4

inout wire hps_usb1_D5, // .hps_io_usb1_inst_D5

inout wire hps_usb1_D6, // .hps_io_usb1_inst_D6

inout wire hps_usb1_D7, // .hps_io_usb1_inst_D7

input wire hps_usb1_CLK, // .hps_io_usb1_inst_CLK

output wire hps_usb1_STP, // .hps_io_usb1_inst_STP

input wire hps_usb1_DIR, // .hps_io_usb1_inst_DIR

input wire hps_usb1_NXT, // .hps_io_usb1_inst_NXT

output wire hps_spim0_CLK, // .hps_io_spim0_inst_CLK

output wire hps_spim0_MOSI, // .hps_io_spim0_inst_MOSI

input wire hps_spim0_MISO, // .hps_io_spim0_inst_MISO

output wire hps_spim0_SS0, // .hps_io_spim0_inst_SS0

output wire hps_spim1_CLK, // .hps_io_spim1_inst_CLK

output wire hps_spim1_MOSI, // .hps_io_spim1_inst_MOSI

input wire hps_spim1_MISO, // .hps_io_spim1_inst_MISO

output wire hps_spim1_SS0, // .hps_io_spim1_inst_SS0

input wire hps_uart0_RX, // .hps_io_uart0_inst_RX

output wire hps_uart0_TX, // .hps_io_uart0_inst_TX

inout wire hps_i2c0_SDA, // .hps_io_i2c0_inst_SDA

inout wire hps_i2c0_SCL, // .hps_io_i2c0_inst_SCL

inout wire hps_i2c1_SDA, // .hps_io_i2c1_inst_SDA

inout wire hps_i2c1_SCL, // .hps_io_i2c1_inst_SCL

inout wire hps_gpio_GPIO00, // .hps_io_gpio_inst_GPIO00

inout wire hps_gpio_GPIO37, // .hps_io_gpio_inst_GPIO37

inout wire hps_gpio_GPIO44, // .hps_io_gpio_inst_GPIO44

inout wire hps_gpio_GPIO48, // .hps_io_gpio_inst_GPIO48

inout wire hps_gpio_GPIO61, // .hps_io_gpio_inst_GPIO61

inout wire hps_gpio_GPIO62, // .hps_io_gpio_inst_GPIO62

inout wire hps_key,

inout wire hps_led,

output wire [9:0] fpga_led, // led_pio.export

output wire [14:0] memory_mem_a, // memory.mem_a

output wire [2:0] memory_mem_ba, // .mem_ba

output wire memory_mem_ck, // .mem_ck

output wire memory_mem_ck_n, // .mem_ck_n

output wire memory_mem_cke, // .mem_cke

output wire memory_mem_cs_n, // .mem_cs_n

output wire memory_mem_ras_n, // .mem_ras_n

output wire memory_mem_cas_n, // .mem_cas_n

output wire memory_mem_we_n, // .mem_we_n

output wire memory_mem_reset_n, // .mem_reset_n

inout wire [31:0] memory_mem_dq, // .mem_dq

inout wire [3:0] memory_mem_dqs, // .mem_dqs

inout wire [3:0] memory_mem_dqs_n, // .mem_dqs_n

output wire memory_mem_odt, // .mem_odt

output wire [3:0] memory_mem_dm, // .mem_dm

input wire memory_oct_rzqin, // .oct_rzqin

input wire fpga_spi_0_MISO, // spi_0.MISO

output wire fpga_spi_0_MOSI, // .MOSI

output wire fpga_spi_0_SCLK, // .SCLK

output wire fpga_spi_0_SS_n, // .SS_n

input wire fpga_uart_0_rxd, // uart_0.rxd

output wire fpga_uart_0_txd, // .txd

///////// TFT /////////

output [7:0] TFT_B,

output TFT_BLANK_N,

output TFT_CLK,

output [7:0] TFT_G,

output TFT_HS,

output [7:0] TFT_R,

output TFT_SYNC_N,

output TFT_VS,

output TFT_BL

);

wire hps_0_h2f_reset_n;

wire clk_33m;

wire clk_66m;

wire [7:0] vid_r,vid_g,vid_b;

wire vid_v_sync ;

wire vid_h_sync ;

wire vid_datavalid;

PLL_0002 pll_inst (

.refclk (fpga_clk50m), // refclk.clk

.rst (1'b0), // reset.reset

.outclk_0 (clk_33m), // outclk0.clk

.outclk_1 (clk_66m), // outclk1.clk

.locked () // (terminated)

);

assign TFT_BLANK_N = vid_datavalid;

assign TFT_SYNC_N = 1'b0;

assign TFT_CLK = clk_33m;

assign {TFT_B,TFT_G,TFT_R} = {vid_b,vid_g,vid_r};

assign TFT_VS = vid_v_sync;

assign TFT_HS = vid_h_sync;

assign TFT_BL = 1'b1;

soc_system u0 (

.button_pio_export (fpga_button), // button_pio.export

.clk_66m_clk (clk_66m),

.clk_clk (fpga_clk50m), // clk.clk

.hps_0_h2f_reset_reset_n (hps_0_h2f_reset_n), // hps_0_h2f_reset.reset_n

.led_pio_export (fpga_led), // led_pio.export

.memory_mem_a (memory_mem_a), // memory.mem_a

.memory_mem_ba (memory_mem_ba), // .mem_ba

.memory_mem_ck (memory_mem_ck), // .mem_ck

.memory_mem_ck_n (memory_mem_ck_n), // .mem_ck_n

.memory_mem_cke (memory_mem_cke), // .mem_cke

.memory_mem_cs_n (memory_mem_cs_n), // .mem_cs_n

.memory_mem_ras_n (memory_mem_ras_n), // .mem_ras_n

.memory_mem_cas_n (memory_mem_cas_n), // .mem_cas_n

.memory_mem_we_n (memory_mem_we_n), // .mem_we_n

.memory_mem_reset_n (memory_mem_reset_n), // .mem_reset_n

.memory_mem_dq (memory_mem_dq), // .mem_dq

.memory_mem_dqs (memory_mem_dqs), // .mem_dqs

.memory_mem_dqs_n (memory_mem_dqs_n), // .mem_dqs_n

.memory_mem_odt (memory_mem_odt), // .mem_odt

.memory_mem_dm (memory_mem_dm), // .mem_dm

.memory_oct_rzqin (memory_oct_rzqin), // .oct_rzqin

.reset_reset_n (hps_0_h2f_reset_n), // reset.reset_n

.spi_0_MISO (fpga_spi_0_MISO), // spi_0.MISO

.spi_0_MOSI (fpga_spi_0_MOSI), // .MOSI

.spi_0_SCLK (fpga_spi_0_SCLK), // .SCLK

.spi_0_SS_n (fpga_spi_0_SS_n), // .SS_n

.uart_0_rxd (fpga_uart_0_rxd), // uart_0.rxd

.uart_0_txd (fpga_uart_0_txd), // .txd

.hps_0_hps_io_hps_io_emac1_inst_TX_CLK (hps_eth1_TX_CLK), // hps_0_hps_io.hps_io_emac1_inst_TX_CLK

.hps_0_hps_io_hps_io_emac1_inst_TXD0 (hps_eth1_TXD0), // .hps_io_emac1_inst_TXD0

.hps_0_hps_io_hps_io_emac1_inst_TXD1 (hps_eth1_TXD1), // .hps_io_emac1_inst_TXD1

.hps_0_hps_io_hps_io_emac1_inst_TXD2 (hps_eth1_TXD2), // .hps_io_emac1_inst_TXD2

.hps_0_hps_io_hps_io_emac1_inst_TXD3 (hps_eth1_TXD3), // .hps_io_emac1_inst_TXD3

.hps_0_hps_io_hps_io_emac1_inst_RXD0 (hps_eth1_RXD0), // .hps_io_emac1_inst_RXD0

.hps_0_hps_io_hps_io_emac1_inst_MDIO (hps_eth1_MDIO), // .hps_io_emac1_inst_MDIO

.hps_0_hps_io_hps_io_emac1_inst_MDC (hps_eth1_MDC), // .hps_io_emac1_inst_MDC

.hps_0_hps_io_hps_io_emac1_inst_RX_CTL (hps_eth1_RX_CTL), // .hps_io_emac1_inst_RX_CTL

.hps_0_hps_io_hps_io_emac1_inst_TX_CTL (hps_eth1_TX_CTL), // .hps_io_emac1_inst_TX_CTL

.hps_0_hps_io_hps_io_emac1_inst_RX_CLK (hps_eth1_RX_CLK), // .hps_io_emac1_inst_RX_CLK

.hps_0_hps_io_hps_io_emac1_inst_RXD1 (hps_eth1_RXD1), // .hps_io_emac1_inst_RXD1

.hps_0_hps_io_hps_io_emac1_inst_RXD2 (hps_eth1_RXD2), // .hps_io_emac1_inst_RXD2

.hps_0_hps_io_hps_io_emac1_inst_RXD3 (hps_eth1_RXD3), // .hps_io_emac1_inst_RXD3

.hps_0_hps_io_hps_io_sdio_inst_CMD (hps_sdio_CMD), // .hps_io_sdio_inst_CMD

.hps_0_hps_io_hps_io_sdio_inst_D0 (hps_sdio_D0), // .hps_io_sdio_inst_D0

.hps_0_hps_io_hps_io_sdio_inst_D1 (hps_sdio_D1), // .hps_io_sdio_inst_D1

.hps_0_hps_io_hps_io_sdio_inst_CLK (hps_sdio_CLK), // .hps_io_sdio_inst_CLK

.hps_0_hps_io_hps_io_sdio_inst_D2 (hps_sdio_D2), // .hps_io_sdio_inst_D2

.hps_0_hps_io_hps_io_sdio_inst_D3 (hps_sdio_D3), // .hps_io_sdio_inst_D3

.hps_0_hps_io_hps_io_usb1_inst_D0 (hps_usb1_D0), // .hps_io_usb1_inst_D0

.hps_0_hps_io_hps_io_usb1_inst_D1 (hps_usb1_D1), // .hps_io_usb1_inst_D1

.hps_0_hps_io_hps_io_usb1_inst_D2 (hps_usb1_D2), // .hps_io_usb1_inst_D2

.hps_0_hps_io_hps_io_usb1_inst_D3 (hps_usb1_D3), // .hps_io_usb1_inst_D3

.hps_0_hps_io_hps_io_usb1_inst_D4 (hps_usb1_D4), // .hps_io_usb1_inst_D4

.hps_0_hps_io_hps_io_usb1_inst_D5 (hps_usb1_D5), // .hps_io_usb1_inst_D5

.hps_0_hps_io_hps_io_usb1_inst_D6 (hps_usb1_D6),// .hps_io_usb1_inst_D6

.hps_0_hps_io_hps_io_usb1_inst_D7 (hps_usb1_D7), // .hps_io_usb1_inst_D7

.hps_0_hps_io_hps_io_usb1_inst_CLK (hps_usb1_CLK), // .hps_io_usb1_inst_CLK

.hps_0_hps_io_hps_io_usb1_inst_STP (hps_usb1_STP), // .hps_io_usb1_inst_STP

.hps_0_hps_io_hps_io_usb1_inst_DIR (hps_usb1_DIR), // .hps_io_usb1_inst_DIR

.hps_0_hps_io_hps_io_usb1_inst_NXT (hps_usb1_NXT), // .hps_io_usb1_inst_NXT

.hps_0_hps_io_hps_io_spim0_inst_CLK (hps_spim0_CLK), // .hps_io_spim0_inst_CLK

.hps_0_hps_io_hps_io_spim0_inst_MOSI (hps_spim0_MOSI), // .hps_io_spim0_inst_MOSI

.hps_0_hps_io_hps_io_spim0_inst_MISO (hps_spim0_MISO), // .hps_io_spim0_inst_MISO

.hps_0_hps_io_hps_io_spim0_inst_SS0 (hps_spim0_SS0), // .hps_io_spim0_inst_SS0

.hps_0_hps_io_hps_io_spim1_inst_CLK (hps_spim1_CLK), // .hps_io_spim1_inst_CLK

.hps_0_hps_io_hps_io_spim1_inst_MOSI (hps_spim1_MOSI), // .hps_io_spim1_inst_MOSI

.hps_0_hps_io_hps_io_spim1_inst_MISO (hps_spim1_MISO), // .hps_io_spim1_inst_MISO

.hps_0_hps_io_hps_io_spim1_inst_SS0 (hps_spim1_SS0), // .hps_io_spim1_inst_SS0

.hps_0_hps_io_hps_io_uart0_inst_RX (hps_uart0_RX), // .hps_io_uart0_inst_RX

.hps_0_hps_io_hps_io_uart0_inst_TX (hps_uart0_TX), // .hps_io_uart0_inst_TX

.hps_0_hps_io_hps_io_i2c0_inst_SDA (hps_i2c0_SDA), // .hps_io_i2c0_inst_SDA

.hps_0_hps_io_hps_io_i2c0_inst_SCL (hps_i2c0_SCL), // .hps_io_i2c0_inst_SCL

.hps_0_hps_io_hps_io_i2c1_inst_SDA (hps_i2c1_SDA), // .hps_io_i2c1_inst_SDA

.hps_0_hps_io_hps_io_i2c1_inst_SCL (hps_i2c1_SCL), // .hps_io_i2c1_inst_SCL

.hps_0_hps_io_hps_io_gpio_inst_GPIO00 (hps_gpio_GPIO00), // .hps_io_gpio_inst_GPIO00

.hps_0_hps_io_hps_io_gpio_inst_GPIO09 (hps_usb1_CONV_N), // .hps_io_gpio_inst_GPIO09

.hps_0_hps_io_hps_io_gpio_inst_GPIO34 (hps_eth1_INT_N), // .hps_io_gpio_inst_GPIO34

.hps_0_hps_io_hps_io_gpio_inst_GPIO37 (hps_gpio_GPIO37), // .hps_io_gpio_inst_GPIO37

.hps_0_hps_io_hps_io_gpio_inst_GPIO44 (hps_gpio_GPIO44), // .hps_io_gpio_inst_GPIO44

.hps_0_hps_io_hps_io_gpio_inst_GPIO48 (hps_gpio_GPIO48), // .hps_io_gpio_inst_GPIO48

.hps_0_hps_io_hps_io_gpio_inst_GPIO53 (hps_led), // .hps_io_gpio_inst_GPIO53

.hps_0_hps_io_hps_io_gpio_inst_GPIO54 (hps_key), // .hps_io_gpio_inst_GPIO54

.hps_0_hps_io_hps_io_gpio_inst_GPIO61 (hps_gpio_GPIO61), // .hps_io_gpio_inst_GPIO61

.hps_0_hps_io_hps_io_gpio_inst_GPIO62 (hps_gpio_GPIO62), // .hps_io_gpio_inst_GPIO62

.video_tft_vid_clk (clk_33m), // alt_vip_itc.vid_clk

.video_tft_vid_data ({vid_r,vid_g,vid_b}), // .vid_data

.video_tft_underflow (), // .underflow

.video_tft_vid_datavalid (vid_datavalid), // .vid_datavalid

.video_tft_vid_v_sync (vid_v_sync), // .vid_v_sync

.video_tft_vid_h_sync (vid_h_sync), // .vid_h_sync

.video_tft_vid_f (), // .vid_f

.video_tft_vid_h (), // .vid_h

.video_tft_vid_v ()

);

endmodule

分析综合、分配引脚。最后的RTL图是这样的:

写过VGA显示器驱动的话就能看出这块TFT液晶屏的引脚跟VGA几乎一样,确实连时序都是一样的,所以只要是VGA时序的屏幕理论上都能用本文的方式驱动。

这样SoC-FPGA工程就修改好了,最后将“DE1_SoC_GHRD.sof”文件生成“soc_system.rbf”文件,以备之后使用。

------

### 5.制作Preloader Image

这部分内容小梅哥的教程里也有,这里查缺补漏快速过一下。

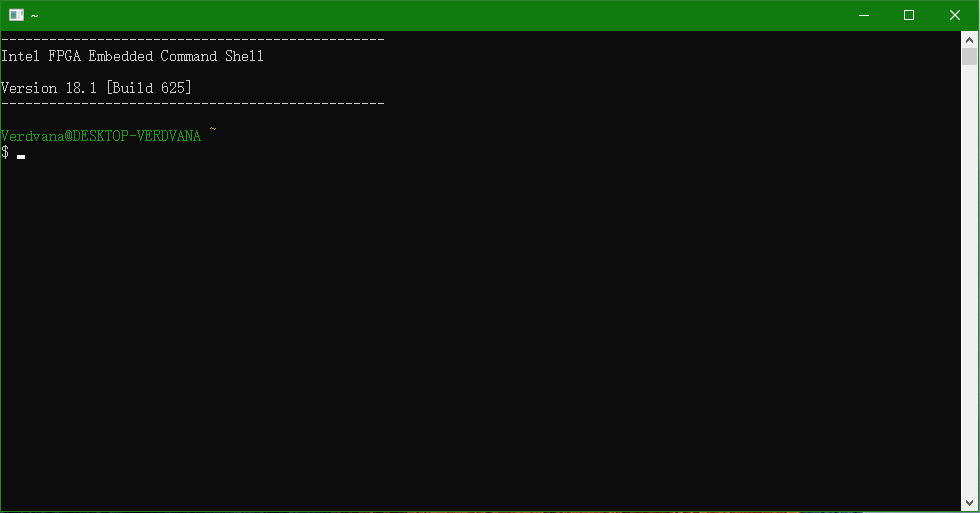

#### 5.1 打开SoC EDS工具

这里注意要用管理员模式打开,不然后面会报错。

#### 5.2 生成bsp文件

在SoC EDS中输入:

bsp-editor

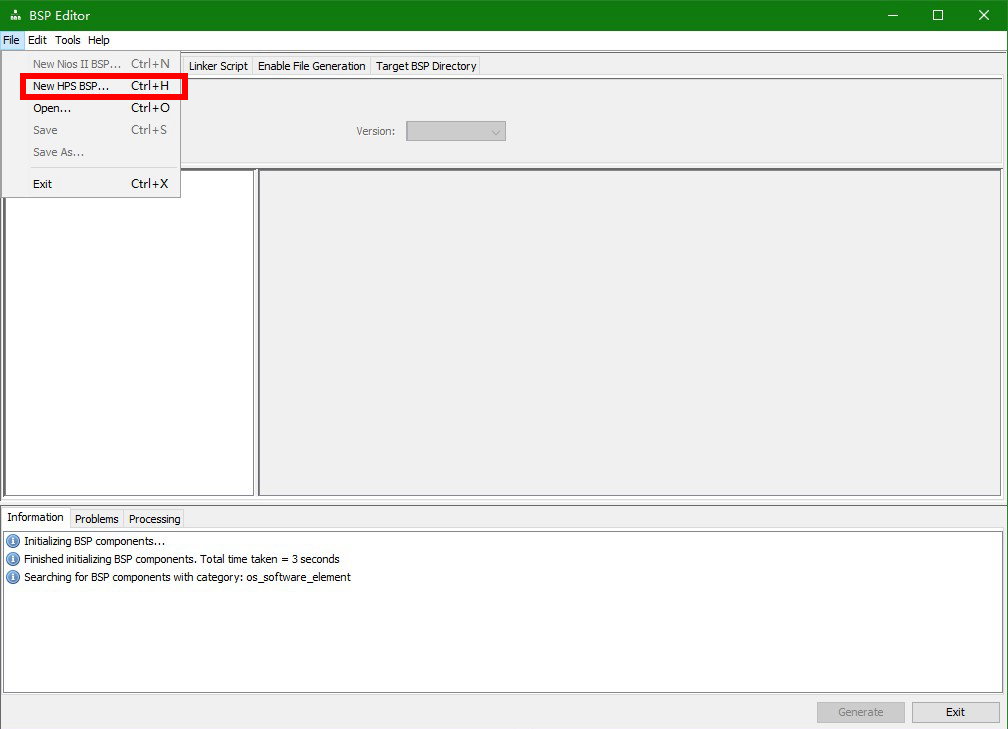

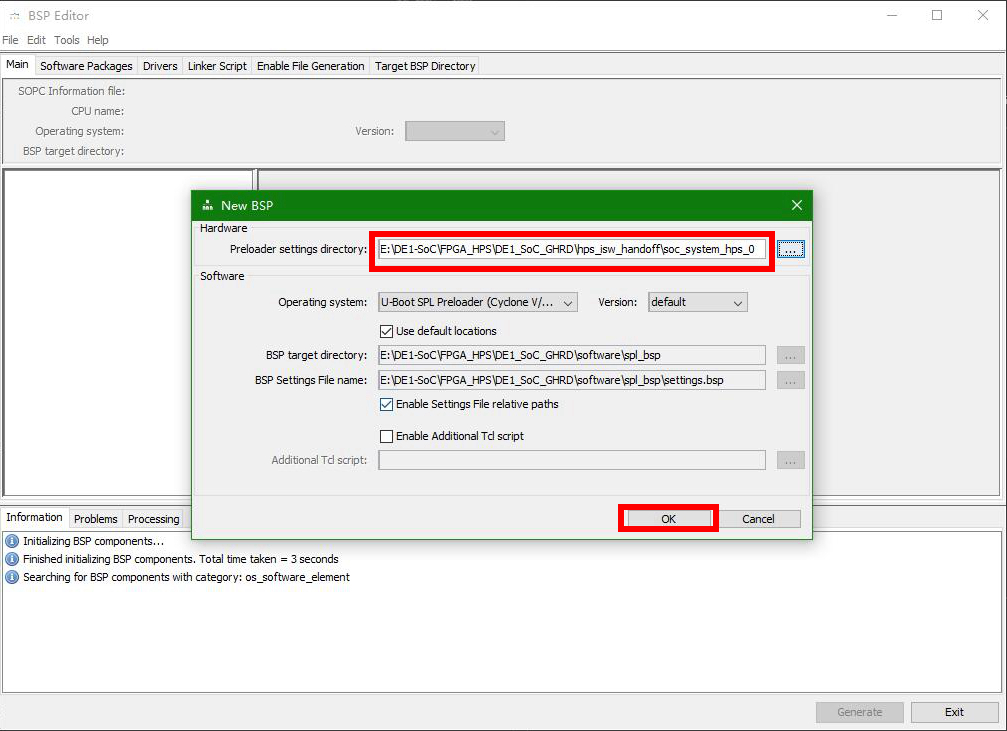

弹出bsp-editor主界面。依次点击 File-->New HPS BSP创建bsp文件,如图:

设定Preloader Setting Directory的路径为:“.. [工程名] hps_isw_handoffsoc_system_hps_0”。比如我的是“E:DE1-SoCFPGA_HPSDE1_SoC_GHRDhps_isw_handoffsoc_system_hps_0”,点击“OK”完成设置。

然后点击“Generate”生成preloader的原始档以及Makfile。生成之后点击“Exit”退出。

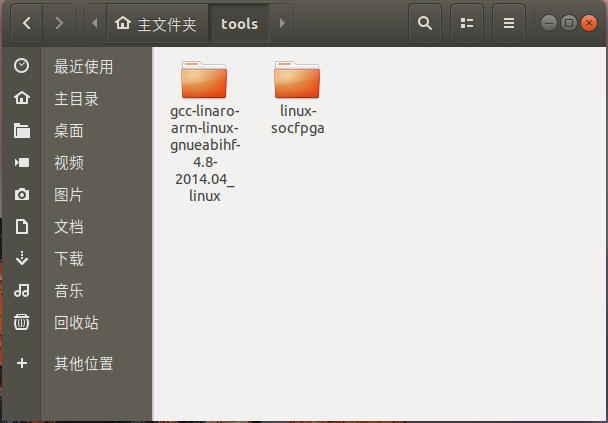

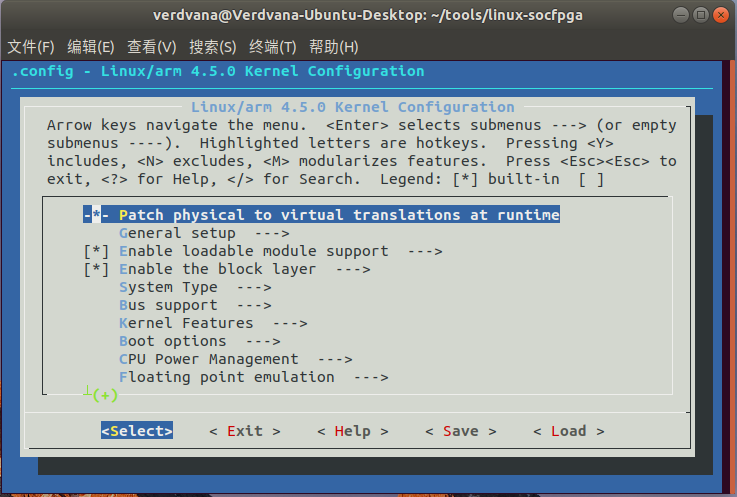

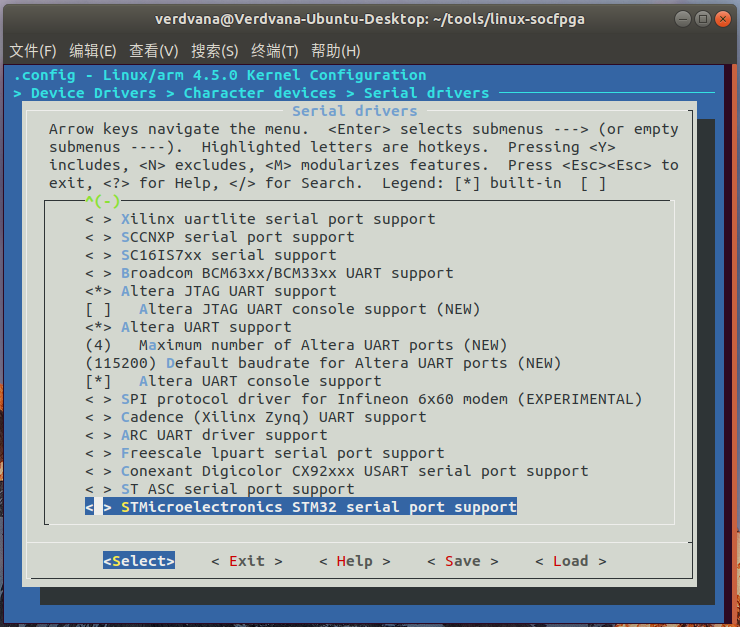

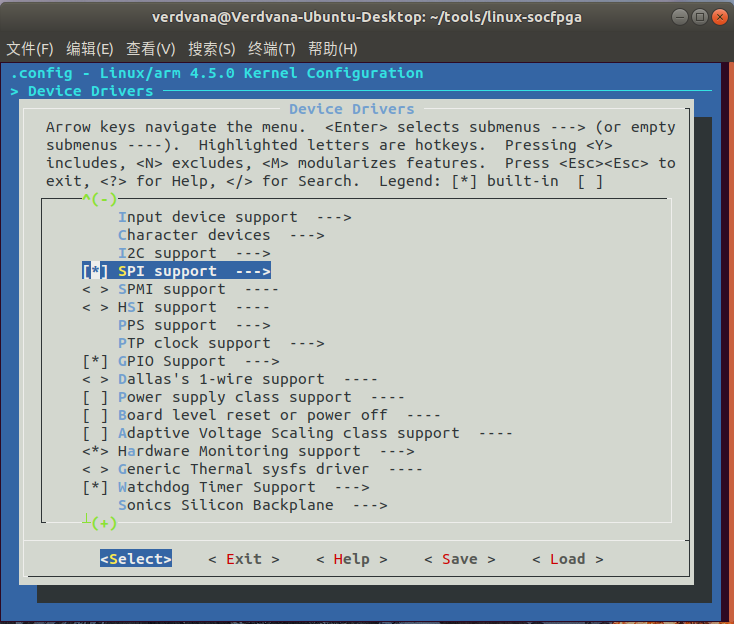

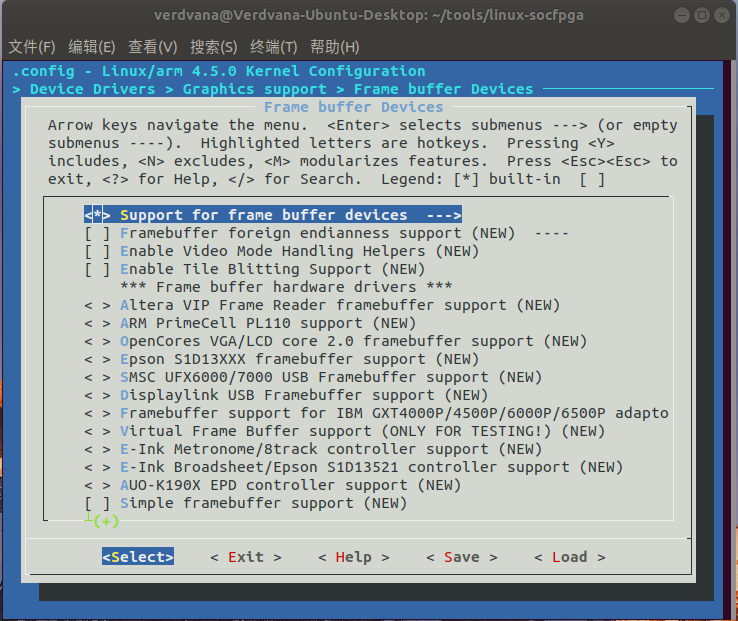

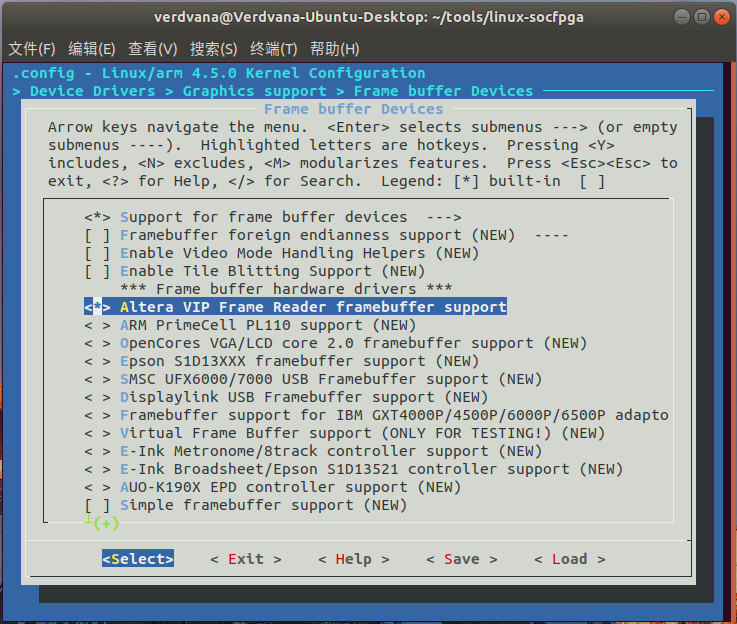

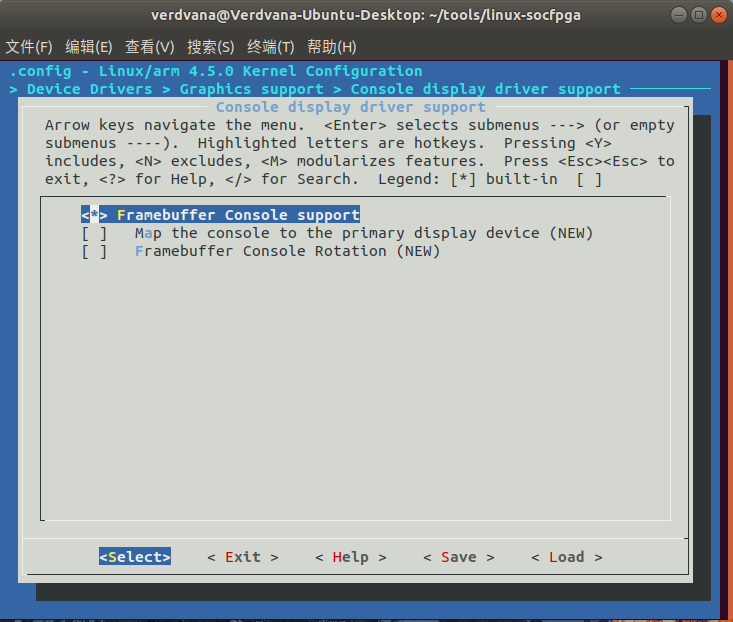

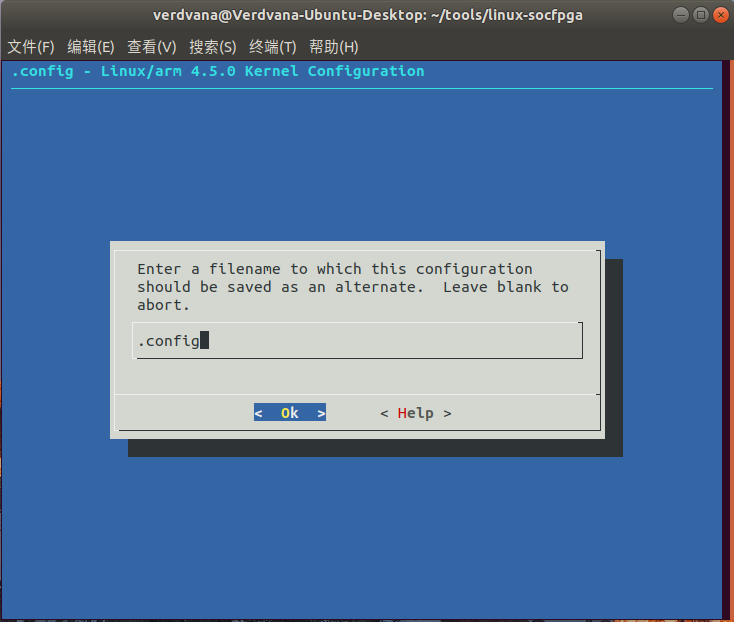

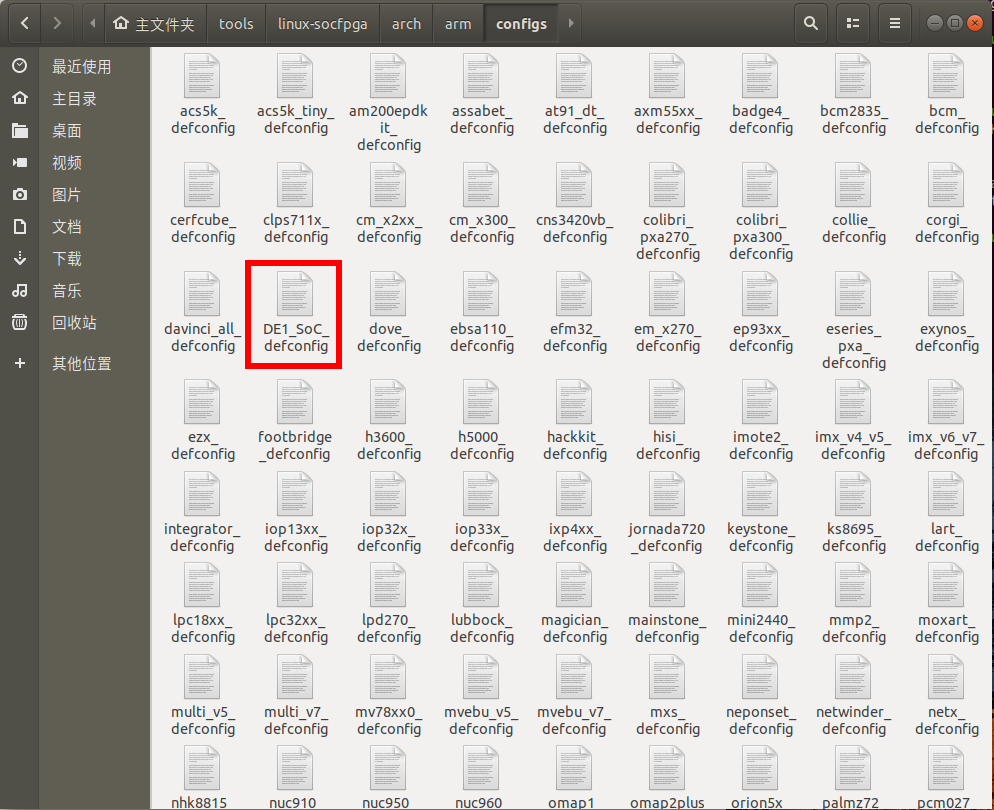

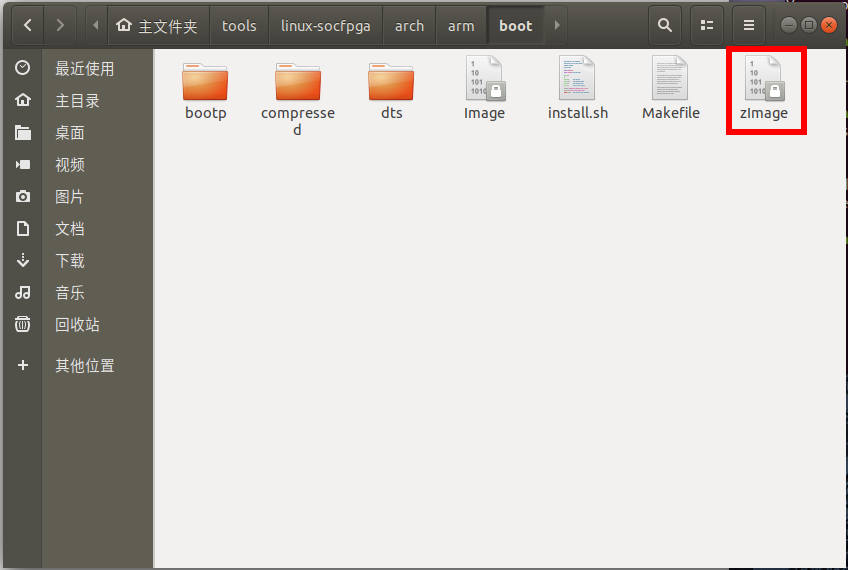

". After solving the problem, enter the following command in the SoC EDS Command Shell to compile: ``` make uboot ``` The process is relatively long, you can play cat for a while to kill time. After the compilation is complete, find the "u-boot.img" file in the "[Project Name]softwarepreloaderuboot-socfpga" path; find the "u-boot-spi.bin" file in the "[Project Name]softwarepreloaderuboot-socfpgaspl" path. Copy these two files to the "[Project Name]softwarepreloader" path. Then use the following command in the SoC EDS Command Shell to enter this path: ``` cd software/preloader ``` Use the mkpimage tool to generate preloader.img, the command is as follows: ``` mkpimage -hv 0 -o preloader.img u-boot-spl.bin ``` At this time, the preloader.img file will appear in your preloader directory. #### 5.4 Update preloader and uboot Insert the DE1-SoC boot SD card into the PC. Determine the drive letter of the partition that can be opened. In my case, it is "J". Enter the following command to complete the update: ``` alt-boot-disk-util -p preloader.img -b u-boot.img -a write -d J //The last letter is the drive letter. Change it according to your personal situation``` If you did not open the SoC EDS as an administrator before, this step will not prompt "Altera Boot Disk Utility was successful". ----- ### 6. Make device tree#### 6.1 Prepare the required files Go to the "..intelFPGA18.1embeddedexampleshardwarecv_soc_devkit_ghrd" path and copy the "hps_common_board_info.xml" and "soc_system_board_info.xml" files to the project path. Enter the following command in SoC EDS Command Shell to return to the project path: ``` cd ../../ ``` #### 6.2 Generate dts file Then enter the following command to generate the dts file: ``` make dts ``` #### 6.3 Generate dtb file Enter the following command to generate the dts file: ``` dtc -I dts -o dtb -fo socfpga.dtb soc_system.dts ``` In this way, the "socfpga.dtb" file is generated in the project path. --------- ### 7. Run the modified project Copy the two files "soc_system.rbf" and "socfpga.dtb" just generated to the SD card to replace the original files. Then eject the SD card and insert it into the DE1-SoC card slot. Plug in Xiaomei's 5-inch TFT LCD screen and press the power button of the development board. You can see that the Linux terminal is displayed on the LCD screen.  However, plugging in a USB keyboard will not input content. This requires modifying the Linux kernel. ----- ### 8. Modify the Linux kernel#### 8.1 Preparation Start the Ubuntu system. Download the Linux system source code: [https://github.com/altera-opensource/linux-socfpga](https://github.com/altera-opensource/linux-socfpga). I chose the same version as Xiaomei: socfpga-4.5. Unzip the downloaded source code to a place. I chose the tools folder in the home directory and changed the file name to "linux-socfpga". Download the compiler: [https://github.com/Verdvana/gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_linux.tar](https://github.com/Verdvana/gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_linux.tar). I also chose the same version as Xiaomei, "gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_linux.tar". Unzip the downloaded compiler next to the Linux source code folder, and do not change the file name.  #### 8.2 Set the cross-compilation environment Shortcut keys "alt" + "ctrl" "t" to open the terminal. Enter the "tools" directory and use the following command: ``` cd ~/tools ``` Open the user initialization file: ``` getit ~/.profile ``` Add the following path to the end of the file: ``` PATH="$HOME/bin:$HOME/.local/bin:$PATH" export PATH=/home/verdvana/tools/gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_linux/bin:$PATH //Change the user name to your own```  Save and exit. Execute the following command to enable the cross-tool to take effect: ``` source /home/verdvana/.profile //Change the user name to your own``` #### 8.3 Configure and compile the kernel Enter the following command to enter the Linux kernel source code directory: ``` cd /home/verdvana/tools/linux-socfpga //Change the user name to your own``` Enter the following command to install related libraries: ``` sudo apt install build-essential sudo apt install libncurses5 sudo apt install libncurses5-dev ``` Specify the hardware architecture: ``` export ARCH=arm ``` Select the default basic configuration provided by the manufacturer: ``` make socfpga_defconfig ```  Open the configuration interface: ``` make ARCH=arm menuconfig ```  Start to configure the kernel. First, enable the Altera UART driver. Go to Device Drivers-->Charater devices-->Serial drivers in sequence, and enter "y" in the "< >" before the Alrera JTAG UART support, Altera UART support, and Altera UART console support options to enable the option.  Then enable the Altera SPI driver. First enter Device Drivers and enter "y" in the "< >" before the SPI support option to enable the option.  Then press Enter to enter this option and enter "y" in the "< >" before the Altera SPI Controller option to enable this option.  Enable the Frame Reader driver. Go to Device Drivers-->Graphics support-->Frame buffer Devices, enter "y" in the "< >" before the Support for frame buffer devices option to enable the option, and other options will pop up.  Enter "y" in the "< >" before the Altera VIP Frame Reader framebuffer support option to enable the option.  In order to support the use of the display as a console terminal, you also need to enable the Framebuffer Console support option in the Device Drivers-->Graphics support-->Console display driver support option.  In Xiaomei's tutorial, it is said that you can use the USB keyboard to input commands here, but it does not work in practice. You have to add the USB HIP peripheral driver to use the external keyboard. Enter Device Drivers-->HID support-->USB HID support in sequence, and enter "y" in the "< >" before the PID device support option to enable the option.  Press the ">" key on the keyboard to make "io/master/_posts/%E4%B8%BASoC-FPGA%E6%B7%BB%E5%8A%A0TFT%E6%98%BE%E7%A4%BA%E5%B1%8F%E5%92%8CUSB%E9%94%AE%E7%9B%98/24.png]https://raw.githubusercontent.co ... %AE%E7%9B%98/24.png[/url]) Press the ">" key on the keyboard to make theio/master/_posts/%E4%B8%BASoC-FPGA%E6%B7%BB%E5%8A%A0TFT%E6%98%BE%E7%A4%BA%E5%B1%8F%E5%92%8CUSB%E9%94%AE%E7%9B%98/24.png]https://raw.githubusercontent.co ... %AE%E7%9B%98/24.png[/url]) Press the ">" key on the keyboard to make the<save>” and press Enter to save your settings.  Select “<ok>”. Then keep pressing “ESC” to exit the configuration interface. #### 8.4 Save the kernel configuration file The current configuration is temporarily stored in the .config file. It is a temporary file. In order to facilitate future calls, it needs to be saved in the “linux-socfpga/arch/arm/configs” path. The command is as follows: ``` make savedefconfig && mv defconfig arch/arm/configs/DE1_SoC_defconfig ``` After saving, there will be an additional “DE1_SoC_defconfig” file in the “linux-socfpga/arch/arm/configs” path.  The next time you call the saved configuration file, enter the following command: ``` make DE1_SoC_defconfig ``` #### 8.5 Compile the kernel Enter the following command to switch to the root user: ``` sudo -i ``` Then you need to enter the password to log in to Ubuntu. Enter the linux-fpga path: ``` cd /home/verdvana/tools/linux-socfpga //Change the username to your own``` Use the following command to specify the processor architecture and cross-compilation tool: ``` export ARCH=arm export CROSS_COMPILE=/home/verdvana/tools/gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_linux/bin/arm-linux-gnueabihf- ``` Enter the following command to load the configured kernel configuration file: ``` make DE1_SoC_defconfig ``` Enter the following command to compile the kernel: ``` make ``` The compilation time is also slightly longer, you can take this opportunity to go out for a walk. After the compilation is complete, the "zlmage" file will be generated in the "linux-socfpga/arch/arm/boot" path.  Copy this file to the development board boot SD card, overwriting the original file. Safely eject the SD card, insert it into the development board, power on, plug in a USB keyboard, hey hey, it's done!

Room 1530, Zhongguancun MOOC Times Building,

Block B, 18 Zhongguancun Street, Haidian District,

Beijing 100190, China

Tel:(010)82350740

Postcode:100190

Room 1530, Zhongguancun MOOC Times Building,

Block B, 18 Zhongguancun Street, Haidian District,

Beijing 100190, China

Tel:(010)82350740

Postcode:100190

京公网安备 11010802033920号

京公网安备 11010802033920号

You can see that the Linux terminal is displayed on the TFT screen, and then use the USB keyboard to enter the administrator username "root" to enter the system. The following is a detailed description of how to hang these two peripherals on the SoC-FPGA and add drivers for them in the Linux kernel. Development environment: Quartus Prime Standard 18.1 Operating system: Windows 10 Pro 1809 / Ubuntu 18.04 LTS ------- ### 2. Create a new SoC-FPGA project. You can refer to Xiaomei's tutorial, which is linked above. The built "soc_system.qsys" is as shown below:

You can see that the Linux terminal is displayed on the TFT screen, and then use the USB keyboard to enter the administrator username "root" to enter the system. The following is a detailed description of how to hang these two peripherals on the SoC-FPGA and add drivers for them in the Linux kernel. Development environment: Quartus Prime Standard 18.1 Operating system: Windows 10 Pro 1809 / Ubuntu 18.04 LTS ------- ### 2. Create a new SoC-FPGA project. You can refer to Xiaomei's tutorial, which is linked above. The built "soc_system.qsys" is as shown below:  --------------- ### 3. Add Frame Reader IP core What is Frame Reader IP core, why to add it, how to add it, in my other article "[Add Frame Reader in Quartus Prime 17.1 and above] IP core](

--------------- ### 3. Add Frame Reader IP core What is Frame Reader IP core, why to add it, how to add it, in my other article "[Add Frame Reader in Quartus Prime 17.1 and above] IP core]( The Frame Reader settings are as shown:  The wiring method is as shown in the figure:

The wiring method is as shown in the figure:  Frame Reader and Clocked Video Output are what we have talked about in the previous article. The Clock Bridge provides clocks for these two IPs. Save and generate HDL. #### 4.2 Modify the top-level file The three IPs just added are needed by the TFT screen, so there are more pins to drive the screen. The Clock Bridge just mentioned also needs a 66.6MHz clock, so a PLL needs to be added. : The parameters of the PLL are as shown in the figure below:

Frame Reader and Clocked Video Output are what we have talked about in the previous article. The Clock Bridge provides clocks for these two IPs. Save and generate HDL. #### 4.2 Modify the top-level file The three IPs just added are needed by the TFT screen, so there are more pins to drive the screen. The Clock Bridge just mentioned also needs a 66.6MHz clock, so a PLL needs to be added. : The parameters of the PLL are as shown in the figure below:  The modified top-level file code is: ``` module DE1_SoC_GHRD( input wire fpga_clk50m, // clk.clk input wire [1:0] fpga_button, // button_pio.export output wire hps_eth1_TX_CLK, // hps_0_hps_io.hps_io_emac1_inst_TX_CLK output wire hps_eth1_TXD0, // .hps_io_emac1_inst_TXD0 output wire hps_eth1_TXD1, // .hps_io_emac1_inst_TXD1 output wire hps_eth1_TXD2, // .hps_io_emac1_inst_TXD2 output wire hps_eth1_TXD3, // .hps_io_emac1_inst_TXD3 input wire hps_eth1_RXD0, // .hps_io_emac1_inst_RXD0 inout wire hps_eth1_MDIO, // .hps_io_emac1_inst_MDIO output wire hps_eth1_MDC, // .hps_io_emac1_inst_MDC input wire hps_eth1_RX_CTL, // .hps_io_emac1_inst_RX_CTL output wire hps_eth1_TX_CTL, // .hps_io_emac1_inst_TX_CTL input wire hps_eth1_RX_CLK, // .hps_io_emac1_inst_RX_CLK input wire hps_eth1_RXD1, // .hps_io_emac1_ins t_RXD1 input wire hps_eth1_RXD2, // .hps_io_emac1_inst_RXD2 input wire hps_eth1_RXD3, // .hps_io_emac1_inst_RXD3 inout wire hps_eth1_INT_N, // .hps_io_emac1_inst_RXD3 inout wire hps_sdio_CMD, // .hps_io_sdio_inst_CMD inout wire hps_sdio_D0, // .hps_io_sdio_inst_D0 inout wire hps_sdio_D1, // .hps_io_sdio_inst_D1 output wire hps_sdio_CLK, // .hps_io_sdio_inst_CLK inout wire hps_sdio_D2,// .hps_io_sdio_inst_D2

inout wire hps_sdio_D3, // .hps_io_sdio_inst_D3

The modified top-level file code is: ``` module DE1_SoC_GHRD( input wire fpga_clk50m, // clk.clk input wire [1:0] fpga_button, // button_pio.export output wire hps_eth1_TX_CLK, // hps_0_hps_io.hps_io_emac1_inst_TX_CLK output wire hps_eth1_TXD0, // .hps_io_emac1_inst_TXD0 output wire hps_eth1_TXD1, // .hps_io_emac1_inst_TXD1 output wire hps_eth1_TXD2, // .hps_io_emac1_inst_TXD2 output wire hps_eth1_TXD3, // .hps_io_emac1_inst_TXD3 input wire hps_eth1_RXD0, // .hps_io_emac1_inst_RXD0 inout wire hps_eth1_MDIO, // .hps_io_emac1_inst_MDIO output wire hps_eth1_MDC, // .hps_io_emac1_inst_MDC input wire hps_eth1_RX_CTL, // .hps_io_emac1_inst_RX_CTL output wire hps_eth1_TX_CTL, // .hps_io_emac1_inst_TX_CTL input wire hps_eth1_RX_CLK, // .hps_io_emac1_inst_RX_CLK input wire hps_eth1_RXD1, // .hps_io_emac1_ins t_RXD1 input wire hps_eth1_RXD2, // .hps_io_emac1_inst_RXD2 input wire hps_eth1_RXD3, // .hps_io_emac1_inst_RXD3 inout wire hps_eth1_INT_N, // .hps_io_emac1_inst_RXD3 inout wire hps_sdio_CMD, // .hps_io_sdio_inst_CMD inout wire hps_sdio_D0, // .hps_io_sdio_inst_D0 inout wire hps_sdio_D1, // .hps_io_sdio_inst_D1 output wire hps_sdio_CLK, // .hps_io_sdio_inst_CLK inout wire hps_sdio_D2,// .hps_io_sdio_inst_D2

inout wire hps_sdio_D3, // .hps_io_sdio_inst_D3 提升卡

提升卡 变色卡

变色卡 千斤顶

千斤顶